一、语音信号的数字化

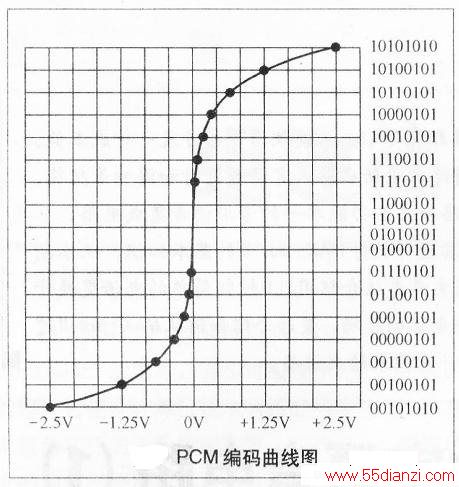

用可编程逻辑器件来设计数字语青电路,前提是先要把语音信号数字化,也就是语音的A/D变换。通常还要对A/D变换后的语音数据进行编码。PCM (脉冲编码调制)技术是一种本的语音数字化编解码技术,在语音通信中得到广泛的应用。我国采用的是A律PCM码,即对A/D变换后的语音信号按照“A律”进行对数式压缩处理,使得8位的PCM码相当于压缩前的13位之线性码,符合G.711标准。还有一种提“μ律”的PCM码,方法略异,主要通行干北美等地。

PC:M编码的特点是,对语音信号按8kHz的速率取样,每次取样得到8bit数据,1 路语音占用64kbit/s的带宽。PCM码的最高位是符号位,其余7位表示语·音振幅绝对值的:大小。为了避免在无语音时出现一长串的“0”

使数据通信难以同步,还要对偶数位进行“反转”处放,如把“00000000”的偶数位取反成为“01010101”来表示实际语音的零振幅,又如用“10101010”和“00101010”分别表示实际语音的正向和负向最大振幅。

PCM编码的示意图见下图,横轴是语音模拟信号的振幅,纵轴是对应的PCM编码。从图中可以看出编码曲线在OV附近 (小信号时)是线性的,能保真语音的细节;随着语音振幅绝对值的增加,曲线变为对数型,扩展了信号的动态范围。

二、PCM编解码器件和信号时序

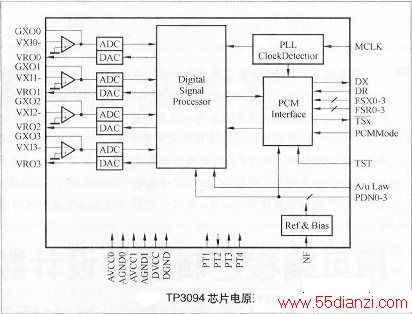

有很多专用集成电路能够完成PCM编解码,美国国家半导体公司的TP3094就是其中一种。TP3094是4路双向PCM编解码芯片,芯片内部的电原理见下图。TP3094的技术文档可从h ttp :// www. national.com/ ds/ TP/TP3094.pdf下载。

PCM 取样时钟的频率是2048kHz。由于 1路语音占用 64k带宽,因此1个PCM的基本信道能够容纳32路语音,称为 1“帧”。这32路语音分时复用传输电路,每路数据每次占用的时间称为 1 个“时隙”。容易算出,时隙的宽度是 1÷32÷8000≈3.9 ( μ s)。有了各自的时隙,32路信号就可以在 1 条信号线上互不影响地分时传输了。

同时收发双向PCM信号时,收、发每32路各占用 1 条信号线。每路语音收/发时,按分配给它的收/发时隙占用收/发信号线。如果要进行语音交换,可以有两种方法:一是在处理电路中把收、发信号线相连,再调整各路收/发时隙的相对位置,如A路收时隙的位置被调到与 B路发时隙一致时,A就收到了B发出的信号,以此类推。该法电路简单,这一讲里用的就是这种办法。二是固定各路的收/发时隙,在处理电路中把发来的各路信号在时间上重新排列后输出供各路接收,如把B时隙来的信号安排到A时隙发回去,A就收到了B的信号。第二种方法更适用于较大容量的语音交换,会在以后讲到。以前一般由标准逻辑电路配合专用集成电路来实现这些功能,现在用PLD能够很灵活地做出这些处理电路来。

三、用P扣设计数字语音电路

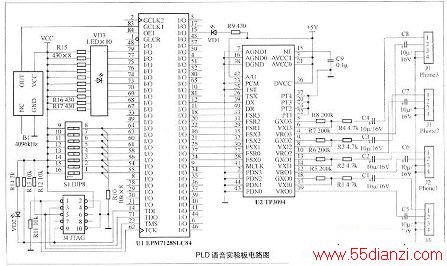

用PLD芯片和PCM编解码芯片设计的数字语音电路见下图。

来自 电话送受话器(即电话手柄,用来试验通话)插座JO—J3的4路双向语音连接到TP3094做编解码处理。TP3094的VXIO-VXI3是各路模拟语音输入踹,连接到电话送话器,电阻R1-R8用来调节各路语音的输人增益。TP3094的VROO-VRO3是各路模拟语音输出端,连接到电话受话器。

电容C1—C8用来隔直流。

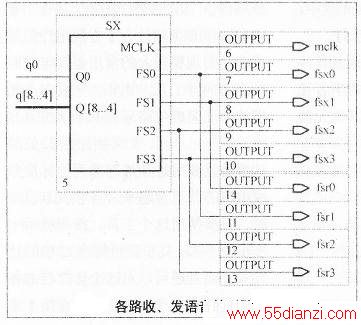

U1是PLD芯片,采用美国ALTEra公司的EPM7128SLC84集成电路。B1是有源晶振,输出4096kHz的时钟信号给PLD。PLD通过内部设计的时序电路输出 2048kHz 的主时钟信号MCLK给TP3094,并产生4个相继的时隙。TP3094的发送时隙是 FSXO-FSX3,接收时隙是FSRO-FSR3,每个收、发时隙都是按应用要求由 PLD的4个时隙之一分配来的,不同的时隙分配状态决定了不同的通话功能。

数字化后的语音从TP3094的DX(数据发送端)送到PLD,经 PLD处理后的数字化语音则送往TP3094的DR (数据接收端)。

S1是8位拨动开关,当开关不通时,与开关连接的PLD各I/0口被电阻RIO拉低,输入“0”信号。反之为“1”信号。通过设置开关能够改变PLD的工作状态。

VD3是10路发光二极管,与其连接的PLD的I/0 口如果输出“0”,则对应的发光二极管亮。通过这些发光二极管可以显示PLD 的工作状态。R15是8路电阻排。

VD1是PLD工作指示灯,当PLD正常时,VD1以每秒1次的频率闪亮。

J4及电阻R11-Rl3组成PLD的JTAG接口,把专用的ByteBlasterMV下载电缆插入JTAG接口,电缆的另一头连接到计算机的并口。当PLD设计完毕后,通过MAX+plusII软件把设计数据下载到PLD芯片对其编程,使PLD具有所设计的功能。VD2是下载指示灯,在下载过程中会闪亮。

由于PLD的可编程性,这个电路不用改变硬件连线就能够设计和试验许多功能,例如:

●PLD工作指示灯●PCM时序电路●语音传输电路●电话监听功能●电话广播功能●信号音发生器●用拨动开关设置PLD状态●10路发光二极管显示●语音交换方式控制●语音音量的动态显示●A律码和线性码的相互转换●语音音量的电平比较●数字语音激活功能这些设计将在本系列文章中陆续介绍,并在各期的配刊光盘中提供相关设计的工程文件。

PLD语音实验板电路完整的Protel设计文件,包括电原理团和印制电路板图,都附在本期配刊光盘中。

四、给PLD加上工作指示灯

在一个既有PLD又有其他元器件的电路里,当出现故障时,初学者往往无法及时判断是PLD还是其他元器件不正常。如果给PLD加上工作指示灯,使PLD正常时指示灯按照一定的规律闪亮,那么只要上电后看到指示灯闪亮,通常就说明PLD没问题。

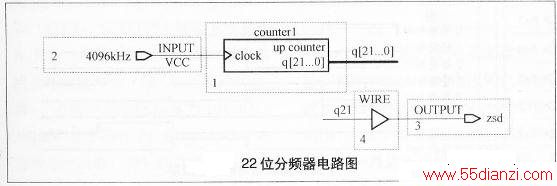

加指示灯的方法很简单,就是把来自B1的4096kHz信号通过PLD进行22次分频,得到lHz的信号输出,点亮发光二极管。

22位分频器电路图见下图,其中counterl是用MAX+plusII软件的“MegaWizardPlug-inManager(功能插件管理器向导)”工具设计的22位分频器。“功能插件管理器向导”是MAX+plusII软件为了方便用户创建自定义的规模较大的常用逻辑电路而设立的向导工具。比如,一般中小规模的标准集成电路只有4位、8位等几种计数器可选用,如果要用到22位的计数器就要用好几片74系列的标准集成电路芯片组合起来,但用PLD设计时,只要使用这个工具,按照提示一步步做下去,几步就可做出22位的计数器,而且还可以对这个计数器的各种参数做选择和修改。我们在接下来的PLD设计中要经常用到这个工具。

把分频得到的秒信号q21通过WIRE连到zsd输出即可点亮PLD工作指示灯。WIRB的作用是连接两个不同名称的端点。

五、用PLO设计PCM时序电路

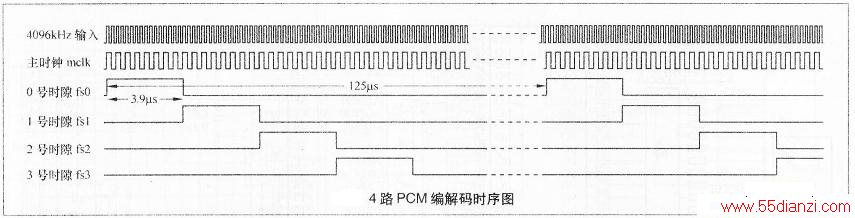

TP3094编解码电路所需繁的主时钟信号mclk、4路时隙信号fs0-fs3的时序关系见下图。为保证信号间相位关系的稳定,这些信号都必须由1司一个时钟源导出。通过PLD内部电路处理输入的4096kHz时钟信号,可以得到下图中的其他信号。

由时序图可见,每个时隙的宽度3.9μs,奸能容纳8个mclk脉冲,对应着8bit的数据;0到3号时隙相继排列但不重叠,表示分时复用;同一时隙的重复周期是125μs,对应着8kHz的取样率。

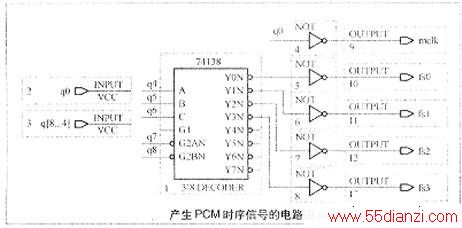

在MAX+plusI1软件中,要得到上图的输出波形,可设计一个产生PCM时序信号的电路,见下图。也可以用AHDL语音(一种简单易学的硬件描述语言)来得到同样的结果。

本文关键字:语音 综合-其它,单元电路 - 综合-其它

上一篇:传统的模拟电压采样保持电路方案