本文先介绍利用这些存储器资源来存储和延迟语音数据的方法,进而实现语音混响的功能。然后介绍QUARTusⅡ软件,说明选用QuartusⅡ软件的理由、Q11artusⅡ软件的一些特点、以及把设计项目从MAX+plusⅡ过渡到QuartusⅡ的方法,并以语音混响电路为例来详细讲解这个移植过程。

一、语音的存储和延时

利用FPGA片内RAM的存储功能,能够把语音数据暂存起来,并在一段时间后再取出存储的语音数据。这样,就可做到语音的存储和延时。

MAX+plusⅡ软件的功能插件管理器里提供了好几种存储器的参数化功能模块,除了普通的RAM、ROM以外,还有FIFO(先进先出存储器)、Dual-pottRAM(双端口RAM)等。这里以FIFO为例做一介绍。

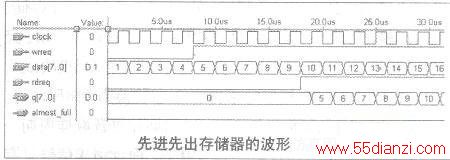

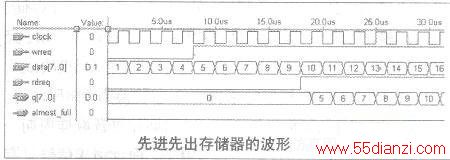

FIFO的特点是数据被写进存储器后,在读数据时总是自动地把先写进去的数据先读出来,图1就是一种FIFO电路的符号。当写请求信号wrreq为高时,数据data【7..0]在时钟cLOCk上升沿的作用下写入存储器;而当读请求信号rdreq为高时,数据在clock上升沿的作用下从存储器的q[7..0]端输出。如果已存入的数据没被读出,存储器满后就存不进新数据了。如上图所示的存储器最多可存2048个8bit的数据,并设计成当存储器里的数据量达到2046个时,存储器发出快要存满的信号almost_full,通过这个信号可使外部电路来读出数据。究竟存了多少数据才认为存储器快满了是可以在设计FIFO时选定的。

FIFO电路的波形仿真图如上图所示。 上图 中当wrreq为高电平时,数据data【7..0】写进FIFO,如果一段时间后rdreq也变成高电平,那么就一边写进新数据一边读出老数据。这一来,数据就被延迟了。如果这是语音数据,就意味着语音被延迟了。

二.语音混响电路

语音混响电路是把语音延迟和衰减后再和来自同一声源的当前语音叠加输出,能够在收听时产生一种空谷回声的效果。

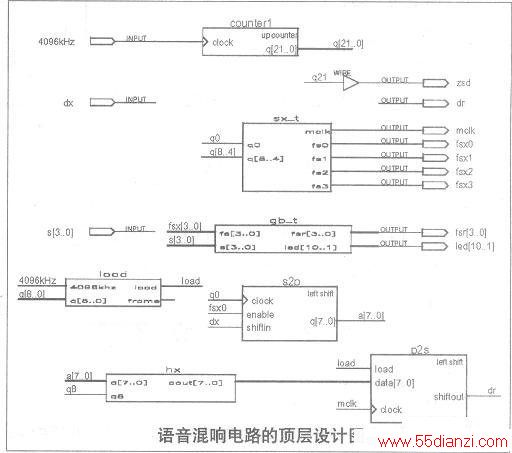

我们在以前语音广播电路的基础上来设计语音混响电路,如上图所示。 上图中0号发送的广播语音经s2p模块转换为并行的A律码语音数据a[7..0],经过一个混响功能模块hx实现语音数据的存储、延时、衰减和叠加,再把混响处理后的A律码数据经p2s模块转换回串行数据输出,使其他用户听到具有}昆响效果的语音广播信号。为进一步了解混响功能模块hx的原理,在MAX+plusⅡ中双击打开hx,它的内部电路如下图所示。

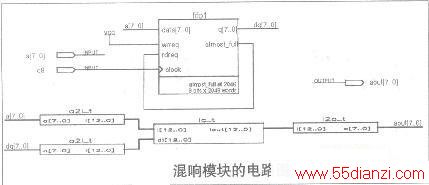

图4中,输入的语音数据a[7..0]分为两路,一路直接送到A律码/线性码转换模块a2l_t,另一路经fifo1存储、延时后输出dq[7..0]到第2个A律码/线性码转换模块。经转换后得到的两路线性码信号都送入线性码控制模块Lc_t,做衰减和叠加运算,运算结果再经12a_t转换为A律码输出。

fifol的时钟由q8担任,使时钟周期和语音取样周期一致。fifoI的写请求信号始终为高电平,而读请求信号只有当:fif01快要存满的信号almost_full出现时才为高电平,这样就延时读出了语音数据。因为语音数据是每125μs取样一次,如选定存到2046个数据时输出almost_full信号,那么就可延时约256ms。

线性码控制模块lc_t的作用是把延时后的语音先作衰减,再与不经延时和衰减的语音相加或相减(取决于两路语音的符号关系)。用AHDI。语言编写的程序如下:

SUBDESIGN lc_t

(1[12..O],dl[12..O]:INPUT;

lout[12..O]:OUTPUT;)

VARIABLE n[11..0]:NODE;

BEGIN

n[8..O]=dl[11..3];

n[11..9]=O;

IF 112= =d112 THEN

10Utl2=112;

lout[11..0]=l[11..0]+n[11..O];

ELSIF

1[11..O]>=n[11..0]THEN

lout12=112:

lOilt[11..O]=l[11..O]-n[11..O];

ELSE

lout12=d112:

lout[11..O]=n[11..O]-1[11..O];

END IF:

END;

两路语音线性码,lout[12..0]是经运算后输出的线性码。n[8..0]=dl[11..3]的含义是把延迟后的语音数据向右移3位,n[11..9]=0的含义是用0填充高3位。二进制数右移1位相当于除以2,右移3位就把信号幅度衰减到只有原来的1/8了。因混响电路对衰减并无精确的要求,采用向右移位法可简化设计。IF语句判别两路输入信号的符号位是否相同以便做对应的运算:同号时输出符号也相同,两路语音相加输出(假定信号幅度适中,相加后没有溢出);异号时则以绝对值大的那路信号的符号作为输出信号的符号,两路语音相减输出。这样,就实现了语音混响的功能。改变fifol的设置和这段程序里的参数可以调整延时时间和衰减系数。

三.学习使用Quartus设计软件到现在为止,我们一直使用着ALTEra公司的MAX+PlusⅡ软件来设计可编程逻辑器件。

MAX+PlusⅡ确实是初学者很好的入门设计软件,有了这个基础,就能够相对容易地过渡到Altera公司当前的可编程逻辑器件主流设计软件--QuartusⅡ。作为AItera公司在MAX+plusⅡ之后推出的新设计软件,QuartusⅡ无疑比MAX+PlusⅡ具有更强大和完善的设计功能,这是使用QuartusⅡ的明显理由。不过对于初学者和可编程逻辑器件的一般使用者来说,使用QuartusⅡ最重要的理由是QuartusⅡ具有支持各种新型可编程逻辑器件设计应用的能力。众所周知,半导体器件每隔几年在集成度和工作速度上都会有成倍的提高,而在功耗和价格方面则有成倍的降低,可编程逻辑器件也不例外。Altera公司在2002年后,就不再推出MAX+PlusⅡ的新版本,因此即使是现有的最新版MAX+PlusⅡ,也不能用来设计2002年后推出的新器件。而这几年去正是CPLD(复杂可编程逻辑器件)和FPGA器件大发展的年代。以Altera公司面向普及型应用的可编程逻辑器件为例,在CPLD芯片方面,推出了新一代的MAXⅡ器件,可取代原MAX系列产品;在FPGA方面,则相继推出了高性价比的Cyclone、CycloneⅡ和CycloneⅢ器件,可取代原FLEX和ACEX系列的产品。如果大家在新产品的设计中要用到可编程逻辑器件,必然希望选用更先进廉价和省电的CPLD或FPGA,这时就需要用QuartusⅡ软件来做设计。这是我们要进一步来学习QuartusⅡ软件的重要原因。

四、Quares的一些特点

那么,QuartusⅡ是否难学呢?QuartusⅡ的界面稍显复杂,但因为我们已经有了使用MAX+PlusⅡ的经验,知道了可编程逻辑器件的设计无非就是根据应用要求输入图形或文本文件、选用和设置库中的一些模块、命名各连线节点和输出入端口、分配器件和引脚、编译、波形仿真、下载设计结果到芯片等等,QuartusⅡ也就是这么一个相仿的设计流程。所以在已经掌握MAX+PlusⅡ用法的基础上再来学习QuartusⅡ并不困难。而且,Altera公司为了帮助原来的MAX+PlusⅡ用户加快熟悉QuartuSⅡ,在QuartusⅡ中还备有一个选项:把图形用户界面设置成类似MAX+PlusⅡ的风格。所以,学习了MAX+PlusⅡ后接着学QuartusⅡ不会困难。

和MAX+PlusⅡ不同的是,用QuartuSⅡ来进行设计,先要建立一个“Project(项目,或称工程)”,QuartuSⅡ自动在项目中建立数据库,围绕项目来组织所有的设计文件,这有点类似于大家比较熟悉的Protel软件。

相比MAX+PlusⅡ来说,QuartusⅡ对中文有较好的支持,项目名、用户库名都可以用中文命名,输入图形和文本时也可用中文来做注释,但输出入引脚,节点、图形符号和文本输入文件不能用中文命名。

在对硬件的支持上,除了个别早期的器件外,在MAX+plusⅡ里能用的器件基本上都能在QuartusⅡ里用。此外,QuartusⅡ还支持M.AXⅡ、Cyclone、APEX、Stratix等系列的新型可编程逻辑器件,支持EPCS系列配置器件,支持ByteBlaster。Ⅱ和USB下载电缆。

QuartusⅡ软件对设计项目作编译时,在逻辑分析和综合、芯片布局布线、时间分析等方面都要进行更多的运算,因此编译时间会长一些,编译过程中产生并实时显示出来的信息也更多。这些信息通常可分成三类:Info(信息)、Warrang(警告)、Error(错误)。对初学者来说,前两类信息可以暂不理会,只要不出现Error就表示编译通过了。如果出现Errot,双击Error的具体条目可定位到出错处,按F1键可得到帮助信息。

在其他功能方面,QuartusⅡ还能够用电源分析工具估算所用芯片的电源功耗(PowerPlay功能),用逻辑分析工具对芯片做逻辑分析(SignalTapⅡ功能),子设计自动化)软件工具如FPGACompiler、ModelSim等交换设计文件。QuartusⅡ在库中提供了更多的功能插件,甚至连CPU都能做到FPGA芯片里去(SOPCBuilder功能)。使用者只要人了门,就能一步步深入学习下去。

为便于大家学习应用,本刊得到Altera公司的授权,在本期配刊光盘中提供了QuartusⅡ6.1的Web版软件。把它安装好,再到Altera公司的网站www.altera.com做个登记,申请许可(LICense)后就能使用。许可是有时间限制的,但可以通过“Update(更新)”继续得到许可。光盘中还提供了中文版的“QuartusⅡ简介”,读者可结合自己的实际需要选择其中的部分内容参考学习,逐步从入门走向熟练。在本文即将付印时,Altera公司又发布了QuartusⅡ7.0版,能够支持CycloneⅢ等最新的可编程逻辑器件。

本文关键字:语音 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术