本文通过实例指明时序分析的关键在于:对具体时序理解透彻的基础上,具体问题具体分析,不能一味的套用公式,更不是通过走线的等长来解决时序问题。

1. 典型高速器件互连时序模型

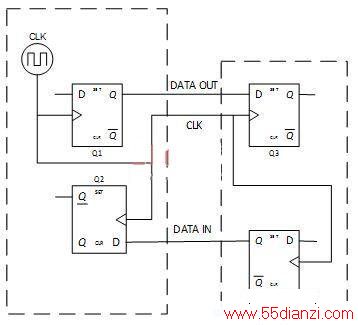

图1给出通用高速器件互连接口简化模型。图中,左侧虚线框表示通信器件双方的主控端。常见的实际情形有:SDRAM控制器、SPI主控制器等。经过适当的演化,基于本模型很容易得到I2C主控端、MII接口的TX组模型、RMII共享时钟模型以及DDR控制信号与地址信号的互连模型等。右侧虚线框表示通信中的被动端。本模型中,数据是双向的,但是时钟是单一方向。简单地说,就是时钟单一方向发送,数据双向传递。这个特点是本模型的适应场景。

图1 简化的器件互连模型

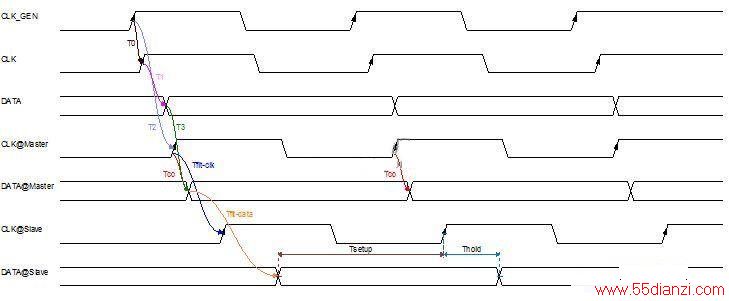

图2 是基于本模型的数据写时序关系图。图中,T0表示主控端内部时钟发生器CLK发出的时钟到达触发器Q1时钟输入端的延时;T1表示触发器Q1接受到时钟后到Q1输出端出现数据的延时;T2表示主控端内部时钟发生器CLK发出的时钟到主控端外部时钟输出引脚的延时;T3表示内部触发器Q1输出的数据到达主控端外部数据输出引脚的延时。通常,半导体制造商不会给出T0-T3这些参数,通常会给出一个用于反映这些参数最终等价效果的参数,即主控端外部数据引脚上出现数据时相对于外部时钟引脚出现时钟信号的延时,这里记为Tco。

图2 数据写时序图

时序分析最关心的参数是信号到达接受端的最终建立时间和保持时间是否符合器件要求。这里将建立时间和保持时间分别记为Tsetup和Thold。Tflt-clk和Tflt-data分别表示时钟信号和数据信号的飞行时间,即他们在对应走线上的延时。Tjitter-clk和Tjitter-data分别代表时钟信号和数据信号上的抖动时间。

器件的建立时间和保持时间是通过描述器件外部的时钟引脚和数据引脚上的时序关系来反映器件内部相关的时序延时和相关目标逻辑时序关系的集总参数。信号从器件的引脚到内部目标逻辑存在一定延时,同时内部逻辑需要最终的建立和保持时间,综合器件内部的这些需求,最终得到器件对外的时序要求。

分析图2中时钟信号和数据信号的相互关系,可以发现:由于Tco的存在,如果器件间的时钟和数据走线等长,则在接收端,用于发送时间的边沿不能用于数据的采样。为了在接收端对数据进行正确采样,必须调整时钟和数据走线的关系,有两种方法:第一,时钟走线长于数据走线,使得数据飞行时间较时钟短。此时,在接收端仍然可以使用产生数据的时钟沿采样数据;第二,数据走线比时钟长,使得数据飞行时间较时钟长。此时,可以使用使用产生数据时钟沿的下一个上升沿采样数据。

实际工程中,设计人员一般使用第二种方法并希望对于数字系统的建立时间和保持时间都留有一定裕量,因此我们可以得出下列公式,即建立时间公式:

(Tsetup)min + (Tco)max + (Tflt-data - Tflt-clk)max + Tjitter-clk+ Tjitter-data < T (1)

和保持时间公式:

(Tco)min + (Tflt-data - Tflt-clk)min - Tjitter-clk- Tjitter-data > (Thold)min (2)

很显然,Tco、Tflt-data 、Tflt-clk中,Tco是器件的固有参数,Tflt-data 和Tflt-clk取决于对应的PCB走线长度和走线层等。如果Tflt-data 和Tflt-clk的差过小,则导致数据的保持时间不足;如果过大,则会使得建立时间不足。因此,Tflt-data 和Tflt-clk的差存在上限和下限双重限制。

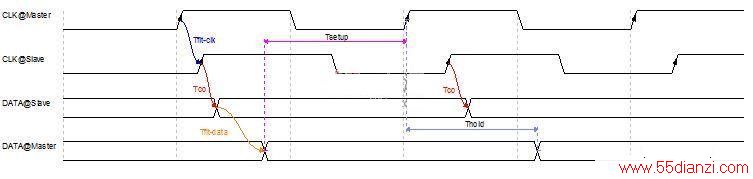

图3 数据读时序图

图3 是基于本模型的数据读时序关系图。图中参数含义与前述相同。需要注意的是:在读关系中,时钟首先需要从主控端传到从端,待从端发出的数据回到主控端后,才能由主控端对数据进行采样。因此,建立和保持时间的公式如下:

(Tsetup)min + (Tco)max + (Tflt-data)max + (Tflt-clk)min + Tjitter-clk+ Tjitter-data < T (3)

(Thold)min< (Tco)min + (Tflt-data)min + (Tflt-clk)max - Tjitter-clk- Tjitter-data (4)

参数Tco、Tflt-data 、Tflt-clk中,To是器件的固有参数,Tflt-data 和Tflt-clk取决于对应的PCB走线长度和走线层等。如果Tflt-data 和Tflt-clk的总和过小,则导致数据的保持时间不足;如果过大,则会使得建立时间不足。因此,Tflt-data 和Tflt-clk的和存在上限和下限双重限制。

需要额外说明的是,前述公式的分析中暗含一个结果,就是:默认器件的输出保持时间和输出延时是等时间的。实际上,不同的半导体器件具有不同的情况,即使同一个半导体器件,在每次输出数据时也不一定是完全相同的。这正是本文开始就一再强调的,时序分析的公式并不是万能的,尽管大多数情况均适用,鉴于现实世界中的情况多样,必须具体问题具体分析。

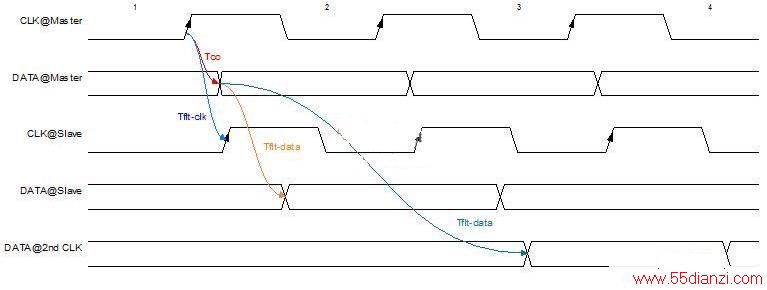

还有一个问题:是否可以使用产生数据时钟沿的次次上升沿采样数据,或者更靠后的边沿来采样数据。图4所示是1#时钟沿发出的数据由3#时钟沿采样的例子,在前述内容中,1#时钟沿发出的数据均由2#时钟沿采样。此处。为了在接收端有较好的建立和保持时间,可以看出数据的飞行时间最好要大于一个时钟周期。假设此时钟周期为40ns,表层走线,板材为FR-4,则数据线的最小长度要635CM。即使时钟周期为8ns,数据线最小长度也要127CM。这显然不是我们所希望的。因此,实际中使用产生数据时钟沿的次上升沿来采样数据。

图4 使用数据产生沿的后续边沿采样数据

2. 时序分析实例

2.1 MII接口

MII接口是最常用的百兆以太网PHY芯片与MAC间的接口,表1和表2分别是某百兆PHY芯片和某MPU内部MAC的RX通道时序参数表。

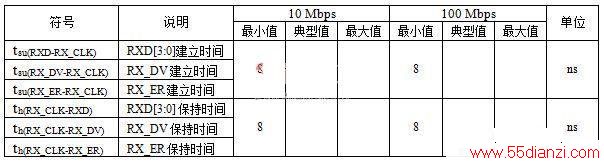

表1 某PHY芯片RX通道时序参数表

表2 某MPU内MAC RX通道时序参数表

通过表格可以看出,MAC侧要求RXD、RX_DV和RX_ER信号对RX_CLK信号的建立与保持时间最小为8ns,也就是实际的建立与保持时间不得小于8ns。假设RXD、RX_DV与RX_CLK信号从PHY侧到MAC侧的延时完全相同,则在MAC侧有:

传输的时钟周期为40ns;

最小的建立时间为40-tval =12ns;

最小的保持时间为thold = 10ns;

最小的建立时间和保持时间总和为22ns;

假设RXD、RX_DV和RX_ER信号对RX_CLK信号存在延时,则存在两种极端情况:

当延时导致建立时间达到最低要求,即当相对延时为+4ns时,则在MAC侧建立时间为8ns,保持时间为14ns;

当延时导致保持时间达到最低要求,即当相对延时为-2ns时,则在MAC侧建立时间为14ns,保持时间为8ns;

假设MII接口走线在PCB表层,PCB板材为FR-4,可知信号传输速度大约为160ps/inch,综合上述两种情况,可以得出RXD、RX_DV和RX_ER相对RX_CLK的走线长度关系为:延迟+4ns时,RXD、RX_DV和RX_ER走线相对RX_CLK可以长:4000/160 * 2.54 = 63CM; 延迟-2ns时,RXD、RX_DV和RX_ER走线相对RX_CLK可以短:2000/160 * 2.54 = 32CM;可见,对于MII的RX通道信号,可以无需考虑等长。

注意,时序关系不代表不需要考虑反射问题。当信号在走线上的传播和返回延时比信号的上升时间长时,就有必要考虑是否进行终端阻抗匹配以抑制反射。

本文关键字:模型 数字逻辑电路,单元电路 - 数字逻辑电路

上一篇:由三极管组成的单稳态电路