下面使用公式进行计算,以对比理论分析和公式法的优劣。为简化计算,忽略公式(1)和公式(2)中的抖动因素Tjitter-clk和Tjitter-data,相关公式变为:

(Tsetup)min + (Tco)max + (Tflt-data - Tflt-clk)max< T (5)

(Tco)min + (Tflt-data - Tflt-clk)min>(Thold)min (6)

将表2和表3中的参数带入公式(5)和公式(6),得出:

10 - (Tco)minflt-data - Tflt-clk< 4

由于PHY芯片参数并没有给出(Tco)min这个参数,所以公式无法得到最终结果。由于PHY芯片的最长输出延时为28ns,最短保持时间为10ns,在此假设(Tco)min为12ns,则:

-2flt-data - Tflt-clk< 4

可分解为:

Tflt-data - Tflt-clk< 4

Tflt-clk -Tflt-data< 2

换算成长度就是:

Lflt-data - Lflt-clk<63CM

Lflt-clk -Lflt-data<32CM

可以看出,使用公式分析时有时会受到参数不全的制约,这时需要根据其他参数推断出需要的参数。对比分析法和公式法,可以看出:分析法比较繁琐,需要认真分析时序关系,而公式法却非常快捷。不过,公式法有时会受到参数的制约,得不到全面的结论。实际中,应该两种方法结合使用。

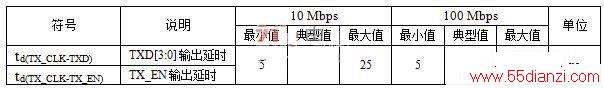

下面分析该PHY芯片和MAC间TX通道的时序。表3和表4分别是该百兆PHY芯片和MPU内部MAC的TX通道时序参数表。

表3 某PHY芯片TX通道时序参数表

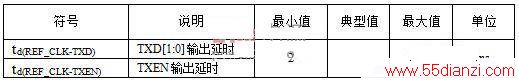

表4 某MPU内MAC TX通道时序参数表

使用公式进行计算,为简化忽略公式(3)和公式(4)中的抖动因素Tjitter-clk和Tjitter-data,则相关公式变为:

(Tsetup)min + (Tco)max + (Tflt-data)max + (Tflt-clk)min< T

(Thold)min< (Tco)min + (Tflt-data)min + (Tflt-clk)max

带入上述参数表中的参数,化简得到:

Lflt-data + Lflt-clk< 47.625CM

假设MII走线在PCB表层,PCB材料为FR-4,走线传输速度为160ps/inch,综合上述分析,可以得出TXD、 TXEN 分别和 TXCLK的走线之和不能大于47CM。实际布线中,本组走线应当越短越好。走线越短,则数据的建立时间越充足,保持时间越少。本实例中,恰好MAC侧允许保持时间为0ns。

2.2 RMII接口

RMII接口也是常用的百兆以太网PHY芯片与MAC间的接口。表5是某百兆PHY的时序参数表,表6和表7分别是某MPU内部MAC的时序参数表。

表6 某MPU内MAC RX通道时序参数表

表7 某MPU内MAC TX通道时序参数表

该MPU内MAC在RMII模式时,不支持时钟输出,同时PHY要求时钟信号为输入。该MPU配合PHY工作在RMII模式下,需要外部使用一颗符合双方精度要求的50MHz振荡器,来为双方提供时钟基准。

为简化时序分析,可以将外部振荡器至MPU和PHY双方的走线设计为等长,此时时钟信号在两者的时钟输入引脚上具有完全一致的时刻。

注意:等长走线的一般实现方法是蛇形线,但等长的蛇形线并不一定意味着等延时。只有当蛇形线的延时效果等同或者尽可能近似于直线时,等长才意味着等延时。为了让蛇形线具有类似于直线的延时效果,蛇形线的高度应尽可能小,蛇形线的开口应尽可能宽,也就是说,波浪线的外形更利于等延时。

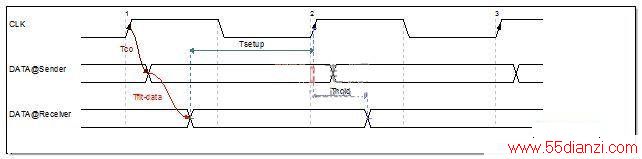

当时钟信号等时刻到达收发双方的输入引脚时,具有如图5所示的时序模型,因而仅需讨论数据线的长度。

图5 共用时钟的RMII时序模型

根据上述时序模型,可得出下列时序公式:

(Tsetup)min + (Tco)max + (Tflt-data)max + Tjitter-clk+ Tjitter-data < T (7)

(Tco)min + (Tflt-data)min - Tjitter-clk- Tjitter-data >(Thold)min (8)

对RXD、CRS_DV和RX_ER信号来说,该组信号由PHY发给MPU,根据公式(7)和公式(8),可得(为了简化,认为最小的Tco时间等于Thold时间):

-1 flt-data < 2

走线时间不可能为负值,假设走线位于PCB表层,材料为FR-4,则:

Lflt-data < 31.75CM

对TXD、和TX_EN信号来说,该组信号由MPU发给PHY,根据公式(7)和公式(8),可得:

-0.5 flt-data < 3

走线时间不可能为负值,假设走线位于PCB表层,材料为FR-4,则:

Lflt-data < 47.625CM

对RXD、CRS_DV和RX_ER信号来说,该组信号由PHY发给MPU。假设数据线走线长度为0,则数据线延时为0ns,此时在MPU侧接受到信号的最小建立时间为:20-14=6ns,最小保持时间为:3ns。MAC侧要求的最小建立时间为4ns,最小保持时间为2ns。可见,此时数据线的走线长度最长延时可以到2ns,此时MAC侧接受到信号的建立时间和保持时间分别为4ns和5ns,符合时序要求。所以走线长度最长可以为31.75CM。

对TXD和TX_EN信号来说,该组信号由MPU发给PHY。假设数据线走线长度为0,则数据线延时为0ns,此时在PHY侧接受到信号的最小建立时间为:20-13=7ns,最小保持时间为:2ns。MAC侧要求的最小建立时间为4ns,最小保持时间为1.5ns。可见,此时数据线的走线长度最长延时可以到3ns,此时MAC侧接受到信号的建立时间和保持时间分别为4ns和4.5ns,符合时序要求。所以走线长度最长可以为47.625CM。

2.3 RGMII接口

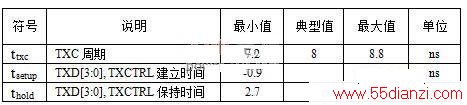

RGMII接口是最常用的千兆以太网PHY芯片与MAC间的接口,表8和表9分别是某千兆PHY芯片和某MPU内部千兆MAC的TX通道时序参数表。该千兆MAC不支持RGMII-ID功能,为简化布线工作,PHY内部双向启用RGMII-ID功能,相关时序参数为RGMII-ID功能使能后的数值。注意,RGMII时序为DDR模式。

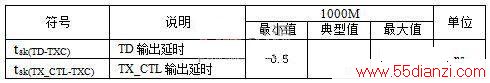

表8 某千兆PHY芯片 TX通道时序参数表

表9 某MPU内千兆MAC TX通道时序参数表

本组数据由MAC发往PHY,为源时钟同步。在PHY端开启内部延时的情况下,要求接受数据的建立时间和保持时间最小值分别为-0.9ns和2.7ns。最差情况下,MPU端发送数据的最小建立时间为-0.5ns,最小保持时间为4-0.5=3.5ns。因此,时钟线和数据线等长是最简单的布线方法。

假设数据信号相对时钟信号存在正延时,为了保证PHY端最小的建立时间-0.9ns,数据最多可以相对时钟延时+0.4ns。最差情况下,有:

PHY侧数据相对时钟的延时为-0.9ns,即建立时间为-0.9ns;

由于数据独立存在期不会低于4-0.5-0.5=3ns,因此保持时间永远不低于3.5ns;

此时,系统整体满足时序要求,数据线可以比时钟线长6.35CM。

本文关键字:模型 数字逻辑电路,单元电路 - 数字逻辑电路

上一篇:由三极管组成的单稳态电路