假设数据信号相对时钟信号存在负延时,为了保证PHY端最小的保持时间2.7ns,由于数据相对于时钟边沿的存在期不短于3.5ns,设数据最多可以相对时钟延时-0.8ns。最差情况下,有:

PHY侧数据相对时钟的延时为0.3ns,即建立时间为0.3ns;

PHY侧数据的保持时间为3.5-0.8=2.7ns;

此时,系统整体满足时序要求,时钟线可以比数据线长12.7CM。

表10和表11分别是该千兆PHY芯片和该MPU内部千兆MAC的TX通道时序参数表。本组时序分析较为简单,很容易分析出数据走线对时钟走线的延时偏差可以为±0.2ns,对于表层走线,FR-4材料,折算成走线长度就是3.175CM。

表10 某千兆PHY芯片 TX通道时序参数表

表11 某MPU内千兆MAC TX通道时序参数表

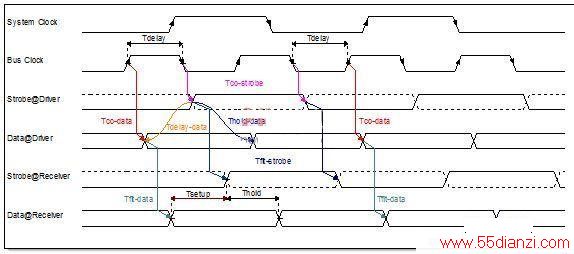

图6是RGMII的时序模型,即DDR模式的时序图。公式(9)和公式(10)是对应的建立时间和保持时间约束公式。公式中, Tstrobe – data表示选通信号相对数据信号的传送延时;Tdata -strobe表示数据信号相对选通信号的传送延时。

图6 RGMII时序模型图

(Tsetup)min< (Tco)min +( Tstrobe - data )min – Tjitter-data – Tjitter-strobe (9)

(Thold)min< (Thold-data)min + (Tdata -strobe)min – Tjitter-data – Tjitter-strobe (10)

将RGMII时序参数表中的相应参数带入公式(9)和(10),可得:

对于RX通道:

Tdata-strobe< 0.4

Tstrobe–data < 0.8

即相当于:

Ldata-Lstrobe< 6.35CM

或

Lstrobe–Ldata< 12.7CM

可见,公式计算结果与理论分析结果一致。TX通道可使用类似方法计算。

2.4 SPI接口

出于成本因素,越来越多的消费电子使用SPI FLASH作为存储器。SPI的通信速度也越来越高。目前,多数MPU都可以支持100M以上的SPI通信速度且支持多I/O通信。

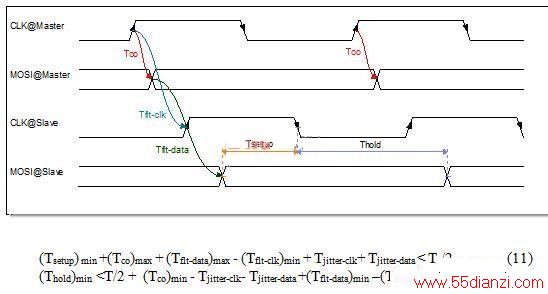

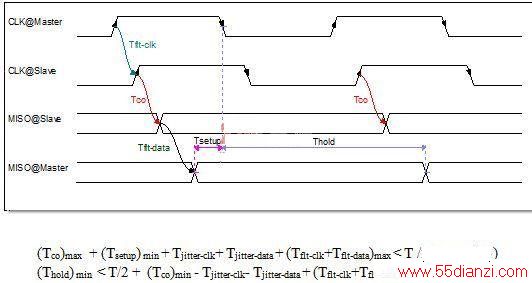

SPI通信的时序关系与前述有所不同,图7和图8分别是SPI在模式1下的数据读时序和数据写时序,公式(11)、公式(12)、公式(13)和公式(14)是对应的时序约束公式。可以看出,由于时序关系的不同,公式也会有所变化。所以,时序分析要具体问题具体对待。

图7 SPI模式1的写时序

图8 SPI模式1的读时序

3. 结论

进行时序分析的关键点首先在于必须对被分析的时序关系非常清楚、能够深刻理解当前对象的时序协议。其次,时序分析要针对具体问题具体分析,不存在所谓的万能时序公式。有时,单纯依靠理论分析或者单纯依靠时序关系公式并不一定能够解决问题,而是要两者结合使用。

对于高速信号的布线而言,存在“等长”说,即很多工程师认为只要所有的线路尽可能等长,就一定满足时序要求。事实上,这是一种错误的认识,本文的实例分析就明确证明了这一点。只有那些时钟和数据由同一个器件发出,由另一个器件接受,并且发送端的建立时间和保持时间恰好满足接收端需求时,“等长”才算是一种偷懒的方法。除此以外,尤其是那些通过单向时钟驱动、采样双向数据或者逆向数据的信号,必须具体问题具体分析。当然,对于PC机这类通用设备来说,由于主板的设计需要兼容不同厂家的内存条,此时走线设计为等长确实是合理的设计。

公共时钟系统由于使用单向时钟信号对双向数据进行采样,因此存在双重限制,两组限制制约了走线不仅有走线长度差值限制,同时还有走线总长度限制。源同步时钟系统使用与数据同向的时钟,因此只存在单重限制,使得走线只有差限制而没有总长度限制。

一般而言,对于SPI接口、MII接口、共享时钟的RMII接口或者SDRAM信号,走线应尽可能的短。对于DDR SDRAM信号以及RGMII等DDR时序的接口来说,多数情况下,组内等长确实是一种简便快速的方法。

本文关键字:模型 数字逻辑电路,单元电路 - 数字逻辑电路

上一篇:由三极管组成的单稳态电路