内容摘要:为满足脑电信号采集、处理设备具有便携式,实时性,数据量大的实际需求,提出了一种基于SOPC的脑电信号实时处理设计方案。用脑电极采集到的脑电信号经过前期预处理(放大,滤波)、A/D模数转换后,经过SOPC系统对脑电信号进行频谱分析、特征提取,最后存储或传输。整个设计围绕SOPC系统,以NiosⅡCPU为核心,并与其他外围设备集成,实现整个系统的控制与处理能力。利用SOPC系统实现的脑电信号采集系统,具有体积小、运算速度快、方案灵活的特点,为构建脑电信号实时处理系统提供了一个新技术方案。

关键词:ADS1258;SOPC;脑电信号;实时处理

脑电信号是人体重要的生理信号,近年来,随着脑机接口的逐步兴起和使用,脑电信号的实时性处理要求也越来越高,脑电信号实时处理的应用,使人们可以直接通过脑来表达想法或操作其他设备,而不需要通过语言或肢体的动作,这对肢体残缺的人来说有着极其重要的意义。

目前,国内外对脑电信号的处理基本上都是基于上位机进行处理。文中提出了一种全新的设计方案:基于SOPC的脑电信号实时处理。SO PC(System on a Programmable Chip)称为可编程片上系统,是基于可编程逻辑器件(FPGA或CPLD)的可重构的SOC。利用FPGA的可编程逻辑资源,按照系统功能需求来添加接口功能模块,既能实现目标系统功能,又能降低系统的成本和功耗。这样就使得FPGA灵活的硬件设计与处理器的强大软件功能有机地结合在一起,高效地实现SOPC系统;同时,嵌入式NiosⅡ软核又可以方便的完成对数字信号处理模块的控制和数据的读写和存储。

1 系统结构

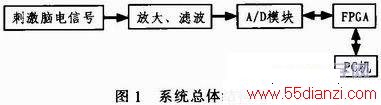

文中的设计系统主要有信号预处理模块、A/D转换模块和数据处理与存储模块3大部分组成。其中A/D转换模块和数据处理与存储模块是基于SOPC系统实现,是本文重点。核心控制芯片采用ALTERA公司生产的CycloneⅡ系列的FPGA,它实现对外围电路的控制和数据的处理与存储。系统总体结构如图1所示。

1.1 信号预处理

脑电信号是很微弱的差模信号,具有低频率,低幅度的特点。并且具有很强的背景噪声和干扰,因此在采集前必须经过必要的预处理,使其达到AD转换的精度要求。所以前端预处理模块有:前置放大器、50 Hz陷波器、高低通滤波器和主放大器等组成。人脑神经活动自发产生的生物电信号通过脑电极进入仪器的前置放大器,在经过低通滤波器滤波,50 Hz陷波器和固定增益放大,最终抑制50 Hz以上的干扰信号,

提取脑电信号。

1.2 设置ADC采样率

本系统选用ADS1258作为模数转换器,ADS1258是TI公司推出的一款高精度、低功耗、低噪声的16通道(多路复用的)24位△-∑型模数转换器(ADC),其内部集成了输入多路复用器、模拟低通滤波器、数字滤波器等功能。内部有多种控制寄存器,用户通过不同的配置得到不同的A/D采样速率、采样模式、A/D转换精度等。

ADS1258在自动通道扫描工作模式下最高转换速率可达每通道23.7 kSPS,是目前转换速率极高的模数转换器;转换时功耗仅42 mW,24位分辨率,可在5 V单电源条件下工作,参考电压可以设置为0~5 V。模拟输入多路复用器可配置成8路差分输入或16路单极输入,多路复用器的输出可通过外部获得,这就能在ADC输入之前采用共享的信号调节通道。使用SPI接口进行功能配置和数据传输,实验证明它能满足信号采集与处理的系统需求。

1.3 FPGA处理

脑电信号传统处理方法有Wigner分布、小波分析、神经网络、非线性动力学以及独立分量,而脑电信号通常还会产生基线漂移和50 Hz交流及高次谐波干扰,因此还需要对信号进行数字滤波,以增强抗干扰能力。与传统的DSP相比,FPGA具有可重构、低成本和低功耗的优势,尤其是在多通道数据的采集和处理上,FPGA利用天然的并行架构,将发挥出一个至几个数量级的优势。ALTERA公司的SOPC Builder可以帮助开发者很容易完成系统的SOPC硬件平台。用户根据已有的硬件系统结构编写信号处理的算法程序,最终在FPGA上实现。

2 SOPC硬件结构

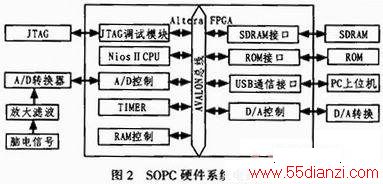

文中的核心控制芯片采用ALTERA公司的CycloneⅡ系列型号为EP2C8020818N的FPGA芯片。该芯片有8 256个逻辑单元,内置18个嵌入式18x18乘法器,2个PLLs,完全满足本设计的需要。此系列芯片支持NiosⅡ32位嵌入式软核处理器,该处理器系统包括一个可配置NiosⅡCPU软核、与CPU相连接的片内外设和存储器以及与片外存储器和外设相连的接口等。所有组件在一个FPGA芯片上实现。SOPC硬件系统结构如图2所示。

整个系统以NiosⅡ软核处理器为主,Avalon总线为核心,各个外设端口挂接在Avalon总线上。通过Avalon总线,NiosⅡ主设备控制各从设备。Avalon总线支持多个总线主外设,允许在单个总线事务中在外设之间传输多个数据单元。这一多主设备结构为构建SOPC系统提供了极大的灵活性,并且能够适应高带宽的外设。

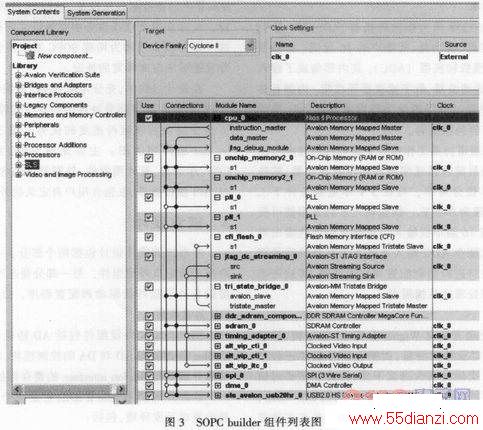

在设计过程中,充分考虑SOPC系统的特色,充分发挥了SOPC系统在数字信号处理中的并行运算优势和NiosⅡ自定义指令加快程序运行速度的优势。图3为本系统的SOPCBuilder组件列表图:主要是用SOPC Builder选取合适的CPU、存储器、及外围器件,外围器件包含系统自带的如定时器,SPI接口核等,也包含用户自定义的外设组件(AD,DA)。

3 软件设计

本系统的软件设计包括两个部分,一部分是基于Verilog的用户自定义外设组件,另一部分是基于NiosⅡIDE开发环境的各外设组件的驱动和配置程序,以及处理脑电信号的FFT算法程序。

用户自定义外设组件包括AD转换和DA转换模块,用Verilog语言编写AD和DA的控制模块,编译、综合后实现其功能并留下与Avalon interface的寄存器接口。

软件开发使用NiosⅡIDE,它是一个基于Eclipse IDE构架的集成开发环境,包括:

1)GNU开发工具(标准GCC编译器、连接器、汇编器和makefile工具等);

2)基于GDB的调试器,包括软件仿真和硬件调试;

3)提供用户一个硬件抽象层HAI。(Hardware Abstraction.Iayer);

4)提供嵌入式操作系统MICroC/OS一Ⅱ和Lwl"CP/IP协议栈的支持:

5)提供帮助用户快速入门的软件模板;

6)提供Flash下载支持(Flash。Programmer和QUARTusⅡProgrammer)。

NiosⅡIDE可以完成NiosⅡ处理器系统的所有软件开发任务。SOPC Builder生成系统后,可以直接使用NiosⅡIDE开始设计C应用程序代码。ALTEra提供外设驱动程序和硬件抽象层(HAL),使用户能够快速编写与低级硬件细节无关的NiosⅡ程序。除了应用代码,用户还可以在NiosⅡIDE工程中设计和重新使用定制库。

基于C编写的算法程序是脑电信号数字处理的核心程序。该程序包括6个相关文件,分别是math.h,register.h,LF2407.CMD.RIS2X X.UB,process.c和evectors.asm。其中需要用到的数学公式库文件是math.h,CPI_I内部的寄存器及其相关定义文件是re面ster.h,连接命令文件是I~2407.CMD,指示编译器如何进行程序空间和数据空间的分配,系统提供RTS2XX.UB库文件,向量表文件cvectors.asm定义所需的复位和中断向量,process.c主要是完成用户期望的功能,是整个程序的核心部分。

FFT部分算法如下:

相关算法的说明:

1)采样频率Fs根据实际情况调整,仿真时为1 000 Hz;

2)快速傅里叶变换的计算公式为:

![]()

N是傅里叶变换的点数,此处为1 024点。

3)由于只计算相对功率,故在计算功率时没有除点数N;

4)本计算的步长取1 ms,将与采样频率对应,给计算带来方便。

系统软件流程图如图4所示。

本文关键字:电信号 嵌入式系统-技术,单片机-工控设备 - 嵌入式系统-技术