��ͨ������£�ר�ü��ɵ�·(ASIC)�Ǵ�����������Ӧ��ϵͳ���ʦ�����뷽�������ǣ����ASIC��Ҫ�������ƹ��ߣ����������ɱ��ܸߣ���Ҫ�Ѳ�Ʒ��ʱ�������г�ʱ�ͻ�е��ܴ�ķ��ա��ݳ���ͳ�ƣ�����60%��ASIC�������Ҫ����һ�����ϵ����ƣ����²�Ʒ�����Ƴ١��ɱ�Ԥ�㳬֧��

HardCopy II��ϵ�ṹ�����ڱ���ΪHcell�ľ�ϸ���Ⱦ���������ϡ� Hcell֧�ִ�Stratix FPGA������ֲ������ASIC�����������ܶȡ��ɱ������ܺ������ơ�ʹ��HardCopy����������ԭ�е�FPGA�������ߣ����ɹ�ʵ����FPGA�����ϵ�SOPCϵͳͨ���ض��ļ���ֱ����ASICת�����Ӷ��˷���ͳASIC������ձ���ڵ�ȱ�㣬�翪�����ڳ�����Ʒ��������һ���Գɹ��ʵ͡�������ͶƬ��Ҫ������������߷����Ұ��������̸��ӵȣ��ǿ��ٿ������ģ�ɱ��ר�ü��ɵ�·(ASIC)ǰ����õķ�չ����

Hardcopy II������Stratix II FPGA����������ȫ���ݡ���оƬ��ʽͶ��֮ǰ���豸�����̿���ʹ��FPGA�����豸С��ģ����������Stratix FPGA����ƽ��в��ԣ�Ȼ��������Ľ��������ֲΪ�ͳɱ������ܵȼۡ����ż��ݵ�HardCopy II ASIC������

1 ����SOPC������Stratix FPGA�Ŀ���

����Stratix FPGAʵʩ���ܶ�����ƣ�����������ڵ��������н���ASICԭ�Ϳ��������������������������ܹ��ܷ����ʹ��Stratix FPGA��ʵ�֣�һ����Ҫ�������ֲΪHardCopy�ṹ��ASIC��

�����Ƴ���Stratix V��HardCopy ASIC���ø�����28 nm�������죬�Ǹ߶��ܶȵ�����ߡ�

Stratix FPGA�Ŀ�������QUARTus II ��������ϵͳӲ����ƣ�Quartus II �����ڸ��ܶ�FPGA������ܹ�ʵ�����Ч�ܣ��������ٶ������ơ�Quartus II ��������ͳһ��ƻ����£�һ���������ۺϡ��Ż�����֤���ߣ�ʹ�ý���ʽ���빦�ܣ��봫ͳ�ĸ��ܶ�FPGA������ȣ���Ƶ���ʱ�������˽�70%�������������Ƶ�Ч�ʡ�

Quartus II��������Ӳ����ϵͳ����Ҫʹ��SOPC Builder���ߡ�SOPC Builder��������SOPCϵͳģ�飬Quartus II֧�ֶ�����Ʒ�ʽ����ԭ��ͼ��Ӳ���������Եȣ�Ӳ���������Եķ�ʽ֧��VHDL��Verilog��SOPC Builder�ṩ��������Avalon���ߵ�IP�⣬������һ��������IP���ɻ������û����Ժ����ؽ��Լ���Ƶ�IP���ɵ�SOPC Builder�У�ʵ��������á���Ƕ��DSPϵͳ��

��ʹ��MATLAB/DSP Builder����DSPģ����ƣ�����MATLAB/DSP Builder��Ƶ�DSPģ�����������ģ����Գ�Ϊ��ƬFPGA��·ϵͳ��һ����ɲ��֣�ʵ��һ���Ĺ��ܡ���һ���棬����ͨ��MATLAB/DSP Builder��ΪǶ��ʽ��������Ƹ������������������ָ����ʽ���뵽Nios II��ָ��ϵͳ���Ӷ���ΪNios II ϵͳ��һ���ӿ��豸��������Ƭ��ϵͳ��Ϊһ�塣������DSP Builder��Nios II CPU���û����Ը�����Ŀ�ľ���Ҫ�����������ع����Լ���DSP������ϵͳ��

SOPC Builder�ṩ3��Nios II ���������ˣ��������͡����ͺͿ������ںˣ���ʹ���߸�����ƾ��������ѡ��Nios IIǶ��ʽ��������һ�������û��ġ��������Ƶ�ͨ��RISC(����ָ��ܹ�)Ƕ��ʽCPU������һ����й���Ӧ��ǰ���Ĵ������������������µ���Ʒ����������SOPC���������������������棺

�� Nios II���Ϲ�ҵ�����ķ�չ��������Ӳ�����������������Nios II����Ч�ؽ��������������ɱ�����߲�Ʒ������;Ӳ��������������ܷ����Ӳ�����з��桢��֤������ϵͳ�ṹ�������������ʹ����֤������ͨ����������˳����ʵ�֣�����������ϸ���������Ϣ;������Ӳ����ƵĴ���ʹ�ö�Ӳ���ӿڲ��Ǻ���Ϥ����Ҳ���Խ���ϵͳƽ̨�ļ��ɡ�

�� Stratix FPGA����������ʹ��ALTEra��˾��ϵ��FPGA�����ļ���������������Nios II EDS��Nios IIϵͳ��Ƕ��ʽ�������Ļ��������������ߡ���������������������Nios II IDE����ɣ������༭�����롢������ԡ����غ����С�Nios II IDE���б������ɻ����Լ���ѡRTOS��TCP/IP�⼯�ɡ������ṩ�����������ߣ�ʹ��GNU��������Ϊ��֧�ż��������⣬Nios II IDE������Ƭ�������������ܡ�

Nios II���˼��俪��ƽ̨(Nios II IDE)���������߽���ģ�鹹���ã�ȴ�ֲ�ʧ����ԣ��Դ�������迪������Ӧ����������������Ҫ�����ƣ�Nios II����ƽ̨�ṩ�����¹��ߣ�

��ʱ��Ҫ����̵������㷨���Բ����û�����ָ���C2H���������м���;���Է���İ�ʵʱ����ϵͳμC/OSII��ֲ��Nios II������;֧���û��������裬�������Ƶ�SOPCԪ������Ҫ����ʱ����ʹ��Ԫ���༭��������Ԫ�������ٴα༭��

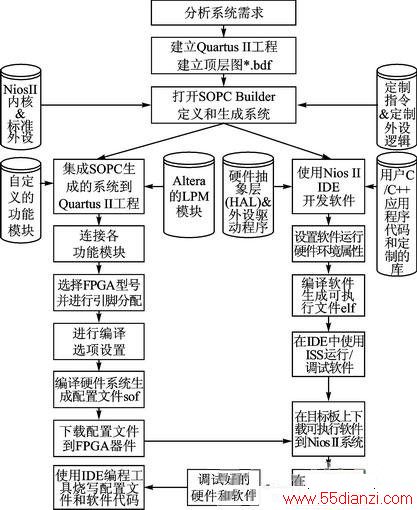

Stratix FPGA���忪��������ͼ1��ʾ��

ͼ1 Stratix FPGA���忪������

2HardCopyϵ����������Ʒ����

HardCopyϵ��������ϵ�ṹ�����ڱ���ΪHcell�ľ�ϸ���Ⱦ���������ϡ�Hcell֧�ִ�FPGA������ֲ������ASIC�����������ܶȡ��ɱ������ܺ������ơ�

HardCopyϵ��������������ԭ�е�FPGA�������ߣ����ɹ�ʵ����FPGA�����ϵ�SOPCϵͳͨ���ض��ļ���ֱ����ASICת�����Ӷ��˷��������ᵽ��ASIC����ձ���ڵ�ȱ�㡣

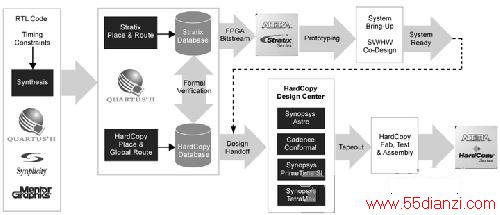

HardCopy ASIC���ж��ص�FPGAǰ����Ʒ�����ʵ����ҵ�������͡���Ʒ�������Ľ������������Stratix FPGA����ƽ��в��ԣ�Ȼ��ALTEra��HardCopy������Ľ��������ֲΪ�ͳɱ������ܵȼۡ����ż��ݵ�HardCopy���������⣬����Altera��˾��HardCopy������Ľ������еIJ�����ƹ�������ˣ�����Ҫ������Ի������ɲ������������Ϳ���������ͼ2��ʾ��

ͼ2 HardCopy ASIC��������

�������е�HardCopy IV ASIC����24���շ�����2��8M~13.3M�Ŀ���ASIC�����Լ�6.3 ~16.8 Mb��Ƭ�ڴ洢���������˶���Ӧ�õ�����HardCopy IV ASIC�ṩ����40 nm�ͺŲ�Ʒ��

�� HardCopy IV GX������Ҫ������Ҫ�����շ�����Ӧ��;

��HardCopy IV E����������Ҫ���������洢���Լ������źŴ���(DSP)���ܵ�Ӧ�á�

���·�����HardCopy V����28 nm�������죬���ܵõ���һ����ߡ�

��֮��Altera HardCopy IV ASICΪ���㶨���������ṩ�ܳɱ���͡�����������Ʒ������졢�������Ľ��������

3 ����

����HardCopy ASIC�滮��ϵͳʵ����������Ӳ��������Эͬ��ƣ����������ϵͳ����ʱ�䣬�ܹ����������档Altera��QUARTus II��������ʹ�ü����Altera�����������֪ʶ��Ȩ(IP)�������û�ͬʱ����FPGA��ASIC��ơ�ֻҪ��Quartus II������ѡ����ʵ�Stratixϵ��FPGA��HardCopy���������Ϳ���������ƣ��dz���

��������Ƴ������ģ���ɵ�·����ҵѹ���������ӡ�����IP���õ�SOPC�����ǽ�������FPGAϵͳ�����ķ���Stratix FPGA���ǻ����������ƽ��п����ģ����Զ�����ʹ��FPGA�����豸С��ģ����;����Ҫ���ģ����ʱ���ڶ�ʱ���ڣ�ͨ��Altera��HardCopy������Ľ�����Startix FPGA�������ֲΪ�ͳɱ������ܵȼۡ����ż��ݵ�HardCopy II�ṹ��ASIC����Ϊ�����ܡ����ġ��ܳɱ��͡���Ʒ�������ڶ̵�ASIC��������δ���߶˸��ӿɱ�̴��ģASIC��ҵ��÷�չ�ķ���

���Ĺؼ��֣����� ���� DSP/FPGA��������Ƭ��-�����豸 - DSP/FPGA����