扭振(即扭转振动)广泛存在于各种回转轴系中,如内燃机曲轴、发电机、齿轮传动链等。就内燃机轴系而言,严重的扭振会导致动力装置的部件断裂,造成不可估计的财产损失和人员伤亡。因此对扭振的动态测量和监控一直为人们所重视。

目前按照对扭振信号的提取方式,扭振测量可以分为模拟式、数字式和软件式。数字式扭振监测应用较为广泛。这一类仪器测量精度较高,信号采集主要用单片机或单片机及 CPLD 。单片机采集信号速度低且系统实时性较差;用单片机结合CPLD实现,系统可扩展性不好,一旦硬件做成很难改动,另外可编程器件与单片机接口的速率匹配也是一个瓶颈问题。

SOPC (System On Programmble Chip)是ALTEra公司提出的片上可编程系统解决方案。它将CPU、存储器、I/0接口、DSP模块、低电压差分信号( LVDS )技术、时钟数据恢复技术(CDR)以及锁相环(PLL)等系统设计所必需的模块集成到一片FPGA上,构成一个可编程的片上系统,使所设计的电路在其规模、可靠性、体积、功耗、上市周期、开发成本、产品维护及硬件升级等多方面实现最优化。用SOPC技术实现扭振信号监测,在测量精度、数据传输及计算、系统扩展等方面都有很大优势。

1 扭振监测原理及方法

轴系在旋转时若没有扭振,则轴的各瞬时速度都等于其平均速度,轴上的齿轮盘也是匀速转动,且传感器输出的每齿一个脉冲信号的重复周期是相同的。当轴系发生扭振时,相当于在轴系平均速度上叠加了一个扭振的波动,于是传感器输出的脉冲序列就不再是均匀间隔了,而是一个载波频率被扭振信号调制的调频信号。这个调频信号可以用脉冲记数法进行解调。设轴系旋转一周的时间为tc,则平均速度为 齿轮的齿数为N,再测出转n个齿的时间为tn,tn在时间内轴系的扭角为

齿轮的齿数为N,再测出转n个齿的时间为tn,tn在时间内轴系的扭角为

因此只要测出tn和tc就可算出相应各£。的扭角θn。

信号的拾取可采用光电编码器。光电编码器由光栅盘和光电检测装置组成,光栅盘是在一定直径的圆板上等分地开通若干个长方形孔。将光电编码器的光栅码盘安装在转轴上,且与转轴同心,当轴系转动时光栅盘与轴同速旋转,经发光二极管等电子元件组成的检测装置输出若干脉冲信号,对脉冲信号计数,并通过计算就可得出θn。

2 扭振信号监测系统的设计及实现

2.1 系统结构及板级硬件设计

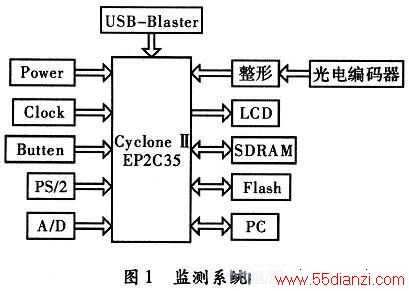

扭振信号测监系统的总体结构,如图1所示。

系统设计采用Altera公司的新一代低成本FP―GA―CycloneⅡ系列的EP2C35实现SOPC系统设计。系统硬件主要包括FPGA上的NiosⅡ处理器系统、FPGA外的接口和外设两部分。NiosⅡ处理器系统由基于 Avalon Bus的NiosⅡCPU、串行接口、PIO、PIO控制器、存储器控制器、定时器以及片上RAM等IP组成。

外设包括:信号拾取整形模块、USB―Blaster-模块、Flash、SDRAM、LCD模块、电源模块、键盘等。信号由光电编码器拾取后经整形模块进入NiosⅡ处理器,CLOCk(系统时钟)模块提供50 MHz有源时钟和用户自定义的外部时钟。上位PC用软件接收RS232发送的连续采样数据,根据规定好的协议,解码出需求的数据进行分析。4个按键开关和PS/2,用于控制信号采样和数据发送,满足用户多种控制要求。系统通过PIO可实现对整形模块、键盘、LCD等外设的控制。存储器控制器分别与片外Flash和SDRAM连接,实现对存储器的访问。

2.2 系统硬件定制

2.2.1 FPGA硬件模块设计

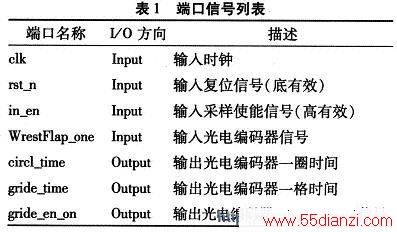

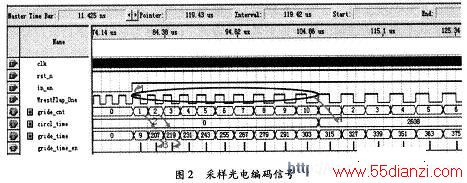

硬件电路板测试完成后,需要设计FPGA硬件模块实现数据采集。模块各端口列表,如表1所示,信号采集仿真波形,如图2所示。输出信号中所有光电编码器时间是系统时钟个数的计数值。最后通过软件模块计算得到平均扭角、瞬时扭角以及误差。

如图2所示,当in_en高有效时,在WrestFlap_one上升沿,寄存器gride_cnt加l,同时gride_time,circl_time开始计算。当下一个WrestFlap_one上升沿时,寄存器gride_cnt加1,直加到一圈格数,然后又重新开始重复的计算。同时当下一个WrestFlap_one上升沿时gride_time输出计算了上一圈的光电编码器一格时间。当gride_cnt一圈数完时,circl_time输出上一圈的总时间。在WrestFlap_one下降沿,gride_en输出使能采样信号,高有效,此信号做为后端 FIFO 写使能信号。(图中椭圆区域为一圈光电编码信号的输出,仿真中规定一圈有10格,第1格对应的gride_time是207,第2格对应的gride_time是219…。)

www.55dianzi.com

2.2.2 SOPC 硬件模块加载及系统构成

在SOPC Builder中进行扭振测量系统配制。添加Ahera自有的丰富IP核,选择SOPC Builder生成HDL代码的类型为Verilog,选择芯片EP2C35,确定系统工作频率,配制处理器选项,定义处理器地址,配制外围设备,安排存储器地址和范围,为外围设备和接口设置所需的中断优先级。同时为优化硬件设计,系统设计了用户自定义外设模块。SOPC Build所用模块如下:

(1)NIOS II Processor CPU;

(2)tri_state_bridge( Avalon 连接总线);

(3)LCD_16207_0(LCD显示);

(4)sdram,cfi_flash(存储器);

(5)button_pio,switch_pio(输入控制端口);

(6)DMA(传输控制)。

2.2.3 用户自定义外设设计

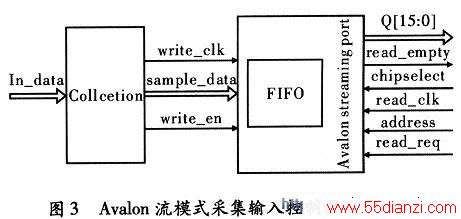

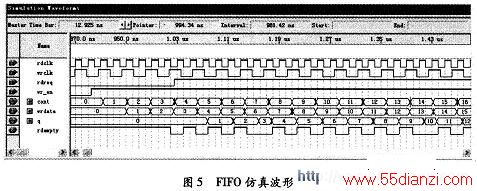

系统设计自定义模块是Avalon流模式采集输入控制器。该控制器设计符合Avalon总线规范,功能是将采集的数据完整送入SDRAM以便存储以及方便数据处理。系统CPU速率为50 MHz,而采样速率不定,因此需要 FIFO 实现前后传输的连贯性。然后经过DMA传输通道将数据存入SDRAM。Avalon流模式采集输入控制器硬件结构,控制器模块分为采集模块和HFO传输模块两部分。采集模块实现数据的采集,其输入接口有:write_clk(写时钟)、write_en(写使能)与sample_data(16位数据总线)。挂在Avalon总线上的接口有FIFO Q[15:0](数据输出总线)、Chipselect(片选信号)、read_req(读请求信号)、address(Avalon总线地址)read_empty(读空信号)、read_clk(读时钟)。

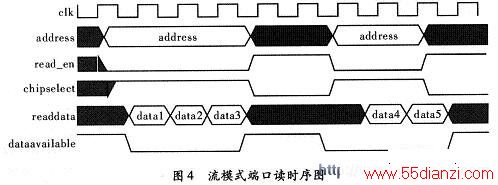

设计使用光电编码每格有效信号作为写使能控制向FIFO写数据,读请求信号read_req由总线发出,经read_empty控制DMA取FIFO中数据的时间,在read_empty低电平期间(即FIFO不空)取FIFO中数据。其时序见图4,其中Dataavailable信号接FIFO输出的空信号(read_empty)。仿真波形,如图5所示。

设计完成后启动SOPC Builder的Generate生成用于综合和仿真的文件,最后在QuarusⅡ中锁定端口引脚,对生成的处理器系统进行仿真、综合、适配并下载到FPGA中。

2.3 系统软件设计

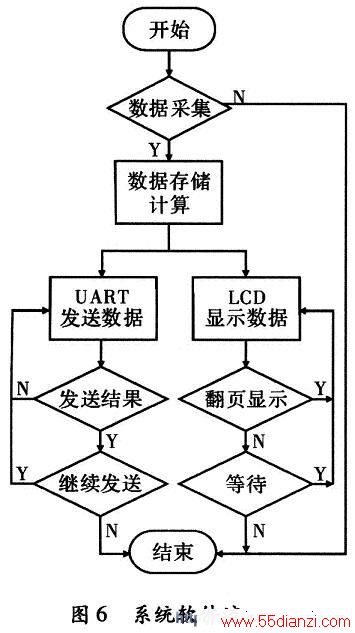

系统软件共有数据采集模块、数据存储计算模块、UART数据发送控制模块和LCD显示控制模块。系统软件流程图,如图6所示,数据采集模块有开关使能。当开关键有效且处于有效采样信号下时,系统开始接收由光电编码器经整形电路采集到的脉冲信号,每次采样信号有效时,采样次数加一,系统共可采集8 000格数据。

本文关键字:测量 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术