乒乓操作的最大特点是,通过“输入数据流选择单元”和“输出数据流选择单元”按节拍、相互配合的切换,将经过缓冲的数据流没有时间停顿地送到“数据流运算处理模块”,被运算和处理。把乒乓看成一个整体,站在这个模块的两端看数据,输入数据流和输出数据流都是连续不断的,没有任何停顿,因此非常适合对数据流进行流水线式处理。所以乒乓方式常常应用于流水线式算法,完成数据的无缝缓冲与处理。

在FPGA里面,使用乒乓操作是面积与速度互换原则的一个体现。

方法2 可以这样实现:在FPGA内部使用Megacore,构造一个双口的RAM, 双口RAM 的输入输出信号的硬件描述语言定义如下:

使用的信号包括:数据信号data_a, dat_b;读写有效信号wren_a, wren_b;地址信号address_a, address_b;时钟信号cLOCk_a,clock_b;输出数据信号q_a,q_b。可以看到所有的信号都是成对出现的,就是为了进行乒乓方式的数据传输。分成了两个RAM区域,A 和B,相当于前面讲乒乓方式里的数据缓冲模块1 和2。两个RAM 块是交替着读写(由I_a和I_b决定),输出数据流也是由I 决定。刚说到写时钟是13.5M,读时钟是27M,所以clock_a 和clock_b必须是读写时钟切换着输入,而且地址的计数也不一样,写周期时候地址增加的时钟是13.5M,读周期地址增加的时钟是27M。所以每行的数据读了两遍,相当于隔行变逐行。图6是在QUARTus II下RAM的乒乓操作功能仿真图:

图6 RAM的乒乓操作仿真图

RAM块进行乒乓方式操作信号的分配表如下:

最后输出的DATA信号进入下一级单元,即YUV到RGB的转换。

2.3 颜色-空间转换部分设计[5]

为什么要有这个转换呢?因为不论是电视机还是CRT显示器,都是使用RGB三基色合成的方法来显示颜色。用RGB三基色来表示彩色的确很直观,但是如果把这种方法用作图像传输则绝不是一个好方法。主要是因为:

(1) 与黑白图像不兼容;

(2) 占用太多带宽;

(3) 抗干扰能力差。

本系统图像传感器输出YCbCr信号,需要进行到RGB信号的转换,用于CRT显示。YCbCr 到RGB按照下面公式进行转换:

R = 1.164 ( Y-16 ) + 1.596 ( Cr-128 );

G = 1.164 ( Y-16 )- 0.813 ( Cr-128 ) - 0.392(Cb-128);

B = 1.164 ( Y-16 ) + 2.017 ( Cb-128 );

观察上面公式可以发现,转换均需要乘加运算,并且式子中用到了小数,所以必须要对系数进行放大。经过合理转化,公式如下:

R = (1/256) * ( 298*Y + 409*Cr - 57065 );

G = (1/256) * ( 298*Y - 100*Cb - 208*Cr + 34718 );

B = (1/256) * ( 298*Y + 516*Cb - 70861 );

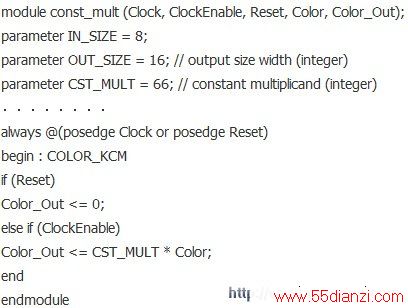

用Verilog HDL编写代码,实现YUV到RGB的转化。其中共包括3个模块跟1个仿真激励。在模块const_mult中,主要实现乘法运算,主要代码如下:

模块csc.v中,调用const_mult模块,通过参数传递改变参数IN_SIZE, OUT_SIZE, CST_MULT的值,然后实现加法运算。

以R = (1/256) * ( 298*Y + 409*Cr - 57065 )为例,主要代码如下:

用以实现G、B的代码与上面类似,在此不再赘述。以下代码实现R_full*1/256功能。

主模块yuv2rgb实现子模块的调用,用Modelsim进行了仿真。仿真波形如图7所示:

图7 YUV到RGB的转化仿真图

3.结论

本文设计了基于 SOPC ">SOPC的 视频编解码 控制器IP核,根据自顶向下的设计思想,将IP核进行层次功能划分,并对IP核的仿真验证,实现了视频信号的采集,分配,存储以及色度空间的转换。本IP核具有很好的移植性,可以方便的应用到以Nios II为核心的各种需要视频编解码控制器功能的嵌入式中。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术