芯片制造商对提高器件性能、降低功耗有着不懈的追求,使得65nm工艺节点面临新的挑战。采用目前最新的技术,ALTEra® Stratix ® III FPGA 利用前一代90nm Stratix II FPGA灵活的逻辑结构,并结合创新的低功耗技术,充分发挥了 QUARTus ® II开发软件中全集成高效基本体系结构的优势。利用Stratix III的内核性能和系统级性能,设计人员不但缩短了设计周期,降低了成本,而且能够以极低的功耗实现大型设计。

本白皮书提供的基准测试数据表明,Stratix III FPGA比前一代Stratix II器件快出25%,详细的体系结构分析显示,Stratix III FPGA的体系结构要比竞争65nm器件快出一个速率等级,逻辑容量是其1.8倍。

引言

按照摩尔定律,随着工艺尺寸的降低,性能和密度在不断提高,但是却很难控制好功耗,难以跟上摩尔定律的预期。为了能够使系统级功耗保持在最低水平上,65nm Altera Stratix III FPGA采用了多种工艺技术,包括Altera专有的可编程功耗技术。Stratix III FPGA的核心结构建立在创新的逻辑单元之上――自适应逻辑模块(ALM)。这种核心结构与MultiTrack互联体系结构相结合,以很少的跳转实现高性能互联,使Stratix III器件能够以非常低的功耗,高效实现高速逻辑、算法和寄存器功能。

体系结构的优势

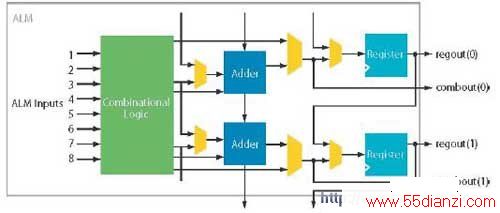

高性能、面积利用率非常高的体系结构的关键所在是ALM,它由组合逻辑、两个寄存器和两个加法器构成,如图1所示。组合部分含8个输入,包括一个查找表(LUT),使用Altera获得专利的LUT技术,查找表可以在两个自适应LUT (ALUT)之间进行划分。一个完整的ALM可实现一个任意6输入功能,但是由于组合逻辑模块有8个输入,因此,一个ALM可以实现两个功能的各种组合。

图1. ALM模块结构

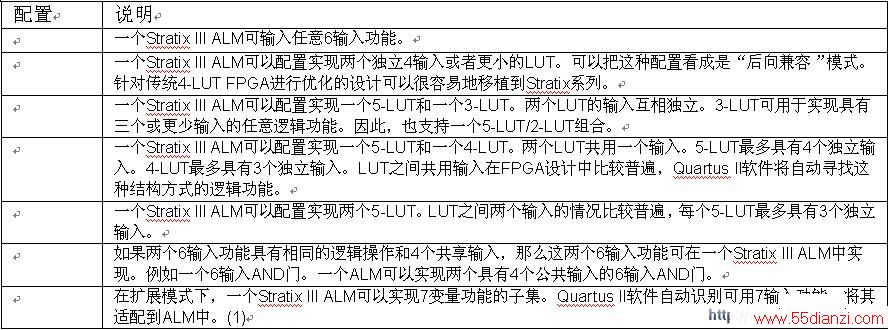

除了能够实现一个完整的6输入LUT,ALM还可以实现两个独立的4输入功能,或者输入都独立的一个5输入和一个3输入功能(表1总结了ALM所支持的组合逻辑配置)。由于可以提供两个寄存器和两个加法器,ALM能够灵活地实现标准4输入LUT (4-LUT)体系结构的2.5个逻辑单元(LE),这一体系结构含有一个4-LUT,进位逻辑和一个寄存器。

f 关于这一体系结构的详细说明,请参考Stratix III器件手册 www.altera.com/literature/hb/stx3/stratix3_handbook.pdf 。

表1. 灵活的ALM

点击看原图

注释:

(1) 请参考Stratix III器件手册( www.altera.com/literature/hb/stx3/stratix3_handbook.pdf ),了解一个ALM可实现的7输入类型的详细信息。

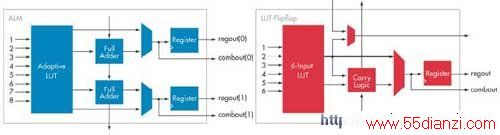

ALM还含有两个寄存器和两个加法器,如图2所示。之所以增加了另一个寄存器,是因为实验表明,许多客户应用需要的寄存器和LUT比高于1:1。两个额外的加法器是为了增强ALM的算术能力,每个ALM可实现两个2位加法或者两个3位加法。因此,ALM要比基本6-LUT的寄存器多一倍,算术能力也提高一倍,是非常优异的构建模块。

ALM在两年前推出,要比最近才推出的Xilinx Virtex-5逻辑单元(也称为LUT触发器对)更灵活,面积利用率也更高。Virtex-5逻辑单元含有一个基本6-LUT、进位逻辑和一个寄存器,如图2所示。作为对比,ALM的组合逻辑部分有8个输入,支持所有的6输入功能,以及其他使用两个输出的大量小功能组合。Virtex-5逻辑单元的组合逻辑部分是基本6-LUT,也有64位CRAM,以及两个输出,这和ALM相似,但是只含有6个输入,实现一个以上逻辑功能的能力有限。其输出之一是6-LUT的输出,另一个是5-LUT,对应RAM配置的下半部分。

图2. Stratix III ALM和Virtex-5 LUT触发器对的对比

尽管基本6-LUT能够实现两个更小的功能,但通常还是只用作一个6-LUT。由于LUT只有6个输入,所需的共享输入数量严格限制了可组合的功能类型。这一限制使得很难将基本6-LUT用作两个5-LUT。作为对比,Stratix III ALM的两个附加输入使其能够用作两个全功能5-LUT,在面积上有很大的优势。

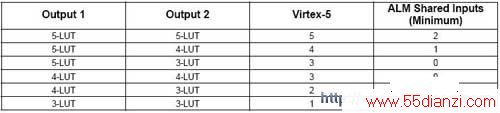

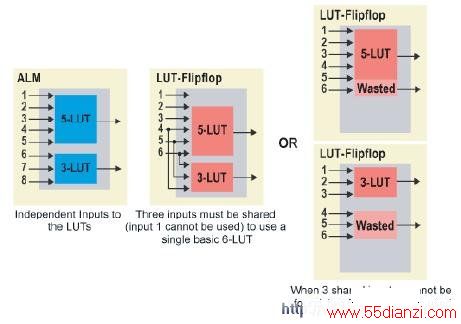

表2给出了几种功能组合所需要的共享输入的数量。例如,ALM能够实现两个独立的4输入功能(没有共享输入),而Virtex-5 LUT需要三个共享输入。图3是另一个例子:ALM能够实现一个5输入和一个3输入功能,不需要任何共享输入,而Virtex-5 LUT需要三个共享输入。很难找到适合Virtex-5 LUT的功能,导致输入少于6个的功能需要占用6-LUT资源才能实现。

表2. Stratix III ALM和Virtex-5 LUT灵活性对比

结合8输入分段式LUT和2:1寄存器至LUT比,ALM能够高效实现两个独立功能,每个需要一个触发器,不需要共享输入或者其他资源。结果,在任何实际设计中,所需要的ALM要少于Virtex-5逻辑单元(参见图3)。

图3. Stratix III ALM和Virtex-5 LUT触发器对实现的5输入和3输入功能

性能基准测试

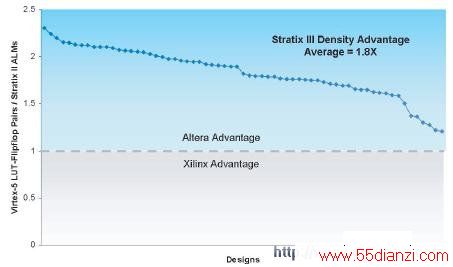

ALTEra在65个真实设计(针对最小面积进行了优化)基础上进行了新的性能基准测试,以比较Stratix III和Virtex-5的性能。性能基准测试提供了Altera ALM和Xilinx LUT触发器对的相对性能平均测量结果。由于具有高效的分段式能力,Stratix III ALM性能平均要比Virtex-5 LUT触发器对高1.8倍。在某些设计中,甚至达到2.3倍,如图4所示。“1”处的水平黑线表示在这一点,Virtex-5 (LUT触发器对)和Stratix III (ALM)的逻辑单元数量相同。

图4. Stratix III ALM和Virtex-5 LUT触发器对性能基准测试对比

注释:

(1) 在最新版ISE设计软件中,针对面积进行优化时,75个客户设计中的10个出现了错误。

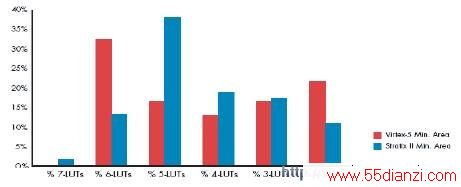

为了更好的理解这些结果,图5显示了由综合产生的LUT分解。图表清晰的显示,Virtex-5器件经过综合,比Stratix III器件产生了更多的6-LUT百分比――32%比13%。这一不同的原因在于,当Virtex-5使用一个基本6-LUT时,由于大部分情况下,不管一个功能需要6个输入还是更少的输入,都要占用整个LUT,因此,Virtex-5需要尽可能多的输入。Virtex-5只能高效实现6-LUT,所以,综合总是尝试产生尽可能多的6-LUT。因为不太可能将两个功能合在一起,共享输入,因此很难建立更小的功能。

图5. 综合期间产生的LUT规模分布

由于LUT具有分段能力,综合工具可以改变LUT规模的分布,产生大小功能合适的组合,因此可以使用更少的ALM。特别是5个以及更少输入的功能只使用一半ALM,因此,只在对速率要求高的逻辑中使用6输入功能便显得非常重要。

ALM可以通过软件优化来灵活地实现。图6所示为 QUARTus II集成综合(QIS)针对三种不同目的(速度、面积和二者平衡)进行优化后产生的三种LUT规模分布。目的不同,LUT规模组合也就不同。当针对速度进行优化时,产生的6-LUT数量最多;针对面积进行优化时,以最少的ALM产生不同的分布。这种灵活性只有Altera能够提供,它源自在体系结构开发过程中,为获得最佳结果,对软件和硬件相互作用进行的深入研究。

f 关于ALM设计和研究的详细说明,请参阅Stratix II FPGA 体系结构白皮书 www.altera.com/literature/wp/wp-01003.pdf 。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术