图6. QIS产生的功能分布

在真实客户设计基础上进行大量基准测试分析,并针对最小面积实施完整的综合、布局布线设计流程后发现,Stratix III ALM“等价于”或者“容纳的逻辑是”Virtex-5逻辑单元的1.8倍(参见表3)。

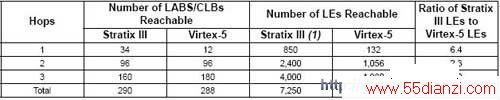

表3. 归一化后的相对逻辑性能

![]()

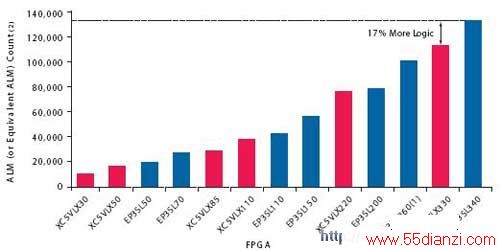

考虑到这一1.8倍的因素,EPSL340器件的逻辑要比XC5VLX330多出17%(参见表4和图7)。

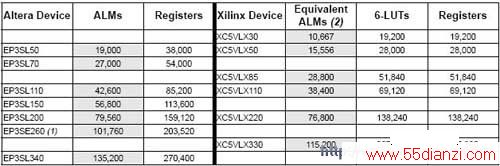

表4. Stratix III和Virtex-5等价器件对比

图7. Stratix III L和Virtex-5 LX逻辑性能对比

注释:

(1) 在这一器件密度上,EP3SE260提供最佳的逻辑、DSP和存储器。

(2) Virtex-5 6-LUT转换至ALM计数时,使用1.8倍因子。

布线体系结构

除了逻辑模块结构之外,另一关键FPGA特性是布线体系结构。Stratix系列器件引入了MultiTrack互联,以实现最佳连接和性能。布线体系结构提供不同逻辑模块群――逻辑阵列模块(LAB)之间的连接,可以通过从一个LAB到另一个LAB的“跳数”对其进行衡量。跳数越少,模式预测性更好,那么性能也就越好,CAD工具也就更容易进行优化。

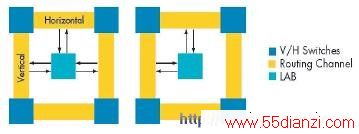

布线结构是大量的行列连线。Stratix系列使用三侧布线结构,如图8所示。这意味着,一个LAB能够驱动上面一个水平通道(H)和左侧、右侧两个垂直(V)通道的所有连线,也可以接受这些通道的驱动。通道中含有长度为4、8、16和24的连线,在连线上任意LAB处都可以下载信号。

图8. 布线体系结构侧面的数量

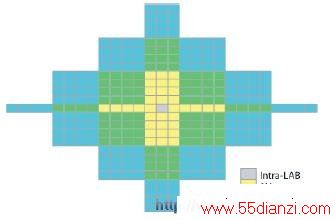

为简单起见,只考虑长度为4的连线,图9显示了从给定LAB(灰色框表示其位置)连接至其他LAB所需要的跳数。

图9. Stratix系列连接

由于可配置逻辑模块(CLB)能够连接至一个垂直通道和一个水平通道(连接至CLB上面一半的连线,以及CLB下面一半的连线)的所有连线,因此Virtex体系结构使用两侧走线体系结构。此外,其连线只能连接至走线部分点的CLB。这些因素限制了连接和布局。采用Virtex-5器件,CLB仍能连接至两个通道,但还是需要L形(在Xilinx材料中指对角)连线来提高互联能力。

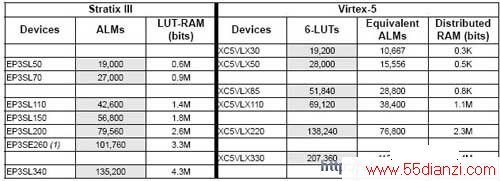

表5对比了在给定跳数情况下, Stratix III系列和Virtex-5能够连接的LAB/CLB数量。在Stratix III器件中,与Virtex-5中的CLB相比,一跳能够到达更多的LAB (34)。如果利用高效的ALM来调整这些数量,结果对Stratix III器件更有利。由于LAB含有等价的25个基于4-LUT的LE,而Virtex-5大约为11个(使用1.8倍因子),如果我们根据这些因素调整在给定跳数内能够到达的逻辑数量,就逻辑性能而言,走线连接情况会更好。

表5. Stratix III和Virtex-5连接对比

注释:

(1) 1个ALM = 2.5个LE,每个LAB = 10个ALM

存储器LAB

Stratix III FPGA 由LAB构成,每个LAB含有10个灵活的ALM,而ALM可配置实现逻辑功能、寄存器功能以及复杂的算术功能。

Stratix III FPGA内核中增加了一种新的LAB――存储器LAB (MLAB)。LAB和MLAB是Stratix III FPGA中的共存对,MLAB ALM可用作普通的LAB ALM,也可以配置为双端口静态随机访问存储器(SRAM),如图10所示。

图10. Stratix III MLAB

LAB的这种LUT-RAM功能可支持最大640位,配置为64×10或者32×20简单双端口SRAM模块,而Virtex-5的CLB只支持64×4配置。SRAM模块经过优化,可以实现滤波延迟线、小容量FIFO缓冲和移位寄存器,最大性能达到650MHz时钟速率。表6对比了Stratix III和Virtex-5系列对应器件,EP3SL340有4.3Mbits的LUT-RAM。

表6. Stratix III和Virtex-5器件的RAM分布

性能优势

Stratix III性能优势包括其独特的内核体系结构以及低功耗技术,内核体系结构可保证系统级时序逼近有足够的性能余量。

内核性能

采用 QUARTus II开发软件中全集成的内核体系结构,可以轻松实现Stratix III器件(该器件是业界速度最快的FPGA)的高性能优势,对设计进行最佳综合,成功实现布局布线,尽快达到时序逼近,帮助设计人员提高效能,同时达到性能目标。

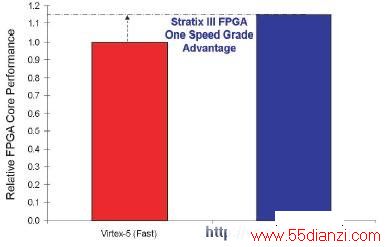

图11显示了来自一组75个真实客户设计的基准测试结果,表明Stratix III器件要比Stratix II器件平均快25%。

图11. Stratix III和Stratix II基准测试

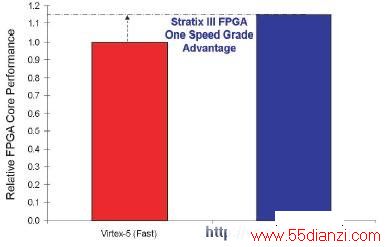

此外,Stratix III FPGA比竞争65nm器件(例如Virtex-5,参见图12)快出一个速率等级。这一平均性能优势基于业界认可的基准测试方法,在一组真实客户设计中使用了带有DSE和Xplorer的最新版Quartus II和Xilinx ISE设计软件,以获得最佳性能结果。

图12. Stratix III和Virtex-5基准测试

更好的系统级性能,并有余量

某些供应商任意规定速率,使用户不得不在实际中对规范进行调整,很难获得最佳性能,而ALTEra在规范上采取了保守的方法。设计人员使用Altera FPGA,可确保轻松实现时序逼近。例如,当Altera说明能够达到333MHz DDR2性能(例如采用Stratix II FPGA)时,实际在所有情况下,设计人员都能保证系统工作在333MHz上。事实上,用户的产品性能甚至可以达到400MHz DDR2。在另一个例子中,Stratix II FPGA在LVDS和DDR2规范上有足够的余量,超过1.25Gbps和400MHz。按照这一趋势,Stratix III FPGA将继续顺利实现系统级时序要求。

要实现更高的系统性能,不但需要很好的内核性能、片内RAM、数字信号处理(DSP)模块,而且还需要对I/O进行优化。Stratix III FPGA的DSP模块和片内RAM (TriMatrix存储器)针对最佳DSP性能进行了全面优化,能够运行在600MHz上。此外,Stratix III FPGA比目前所有的单片DSP处理器的性能高出几个数量级,每秒乘累加运算次数(GMAC)达到537吉。

TriMatrix片内存储器提供三种不同的存储器结构:640位MLAB、9Kbit块(M9K)和144Kbit块(M144K)。这些模块针对最大效率进行优化,MLAB可以放置在器件中的任何地方,非常灵活,能够支持600MHz以上的时钟速率。采用TriMatrix片内存储器和DSP模块,Stratix III器件是视频和图像处理、高速数字通信以及其他高性能DSP应用的理想选择。FPGA内核模块的性能如表7所示。

表7. Stratix III FPGA内核性能

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术