IIC总线是一种应用广泛的通讯接口。它的优点很多。首先,这种接口非常简单,仅须使用SDA(串行数据),SCL(串行时钟)两根数据线便可实现数据传送。由SCL串行时钟进行数据同步,SDA线用来传送八位二进制的串行数据。IIC总线又有着相对完善又不复杂的传输规范。由于IIC总线使用了SCL(串行时钟)进行同步传输,传输速率可随同步时钟变化,丝毫不会到影响数据传输的准确性,只要不超过接收、发送双方的传输速率上限。象较早的异步通讯接口,由于不是同步传输,对传输输率要求就非常严格了,不但要求收发两端必须采用同样的传输速率设置,而且收发两端的时钟差异不能超过5%。IIC总线传输速率一般不超过1MBit/S,适用于对速度要求不是很高的场合,如电视、手机、DVD等各类电子产品之中芯片之间的讯息传递。

IIC总线存储器是一种采用IIC总线接口进行数据存取的可擦除写入存储器件,广泛应用于音视频设备之中。早期产品如M58655、PCF8581等等,现在大多使用24系列存储器件,如电视机中使用的24C02、24C04、24C08等等,用来存储电视机收看节目使用的制式、语言、工作模式及频道数据等信息。

下面以24C02存储器为例,介绍一下IIC总线存储器的数据传输规范以及采用单片机对IIC总线存储器进行数据复制。

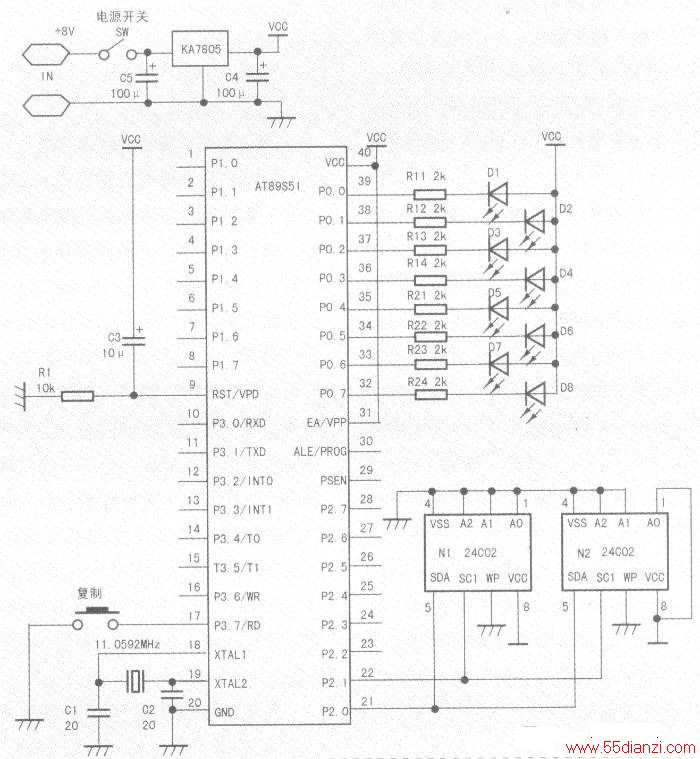

下图即为数据复制仪的电路原理图。这种电路配合下文程序,可完成两片存储器N1、N2之间数据复制。程序设计以N2为读取方,Nl为写入方,完成将存储器N2中的数据复制到N1之中。

电路核心采用单片机电路89S51。一个完整的微机系统必须包括处理器、内存(随机存储器)、ROM(程序存储器)及输入输出接口这几部分。所谓单片机就是将这几部分集成到一块电路中,从而形成一个完整的微机系统,可以独立完成一些较小的程序。现在单片机电路已经很普遍了,遥控电视机中的微处理器就是一种最常见的单片机电路。

单片机电路89S51内部集成了128Byte的随机存储器RAM、4KByte的可擦写程序存储器ROM、P0-P3四个双向输入输出端口、一个标准的异步通讯接口,用来与电脑COM口连接,进行异步通讯。

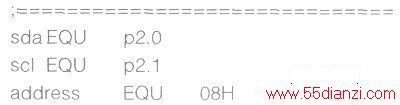

89S51并不具有标准的IIC总线通讯接口,这里仅通过软件模拟,实现与标准IIC总线接口存储器的数据通讯。

存储器N2、N1与单片机89S51通过SDA、SCL两线,共同连接在一条IIC总线之上。N1的三位芯片地址线A0、Al、A2全部接地,N2的AO地址线则与正电源相接。这样的连接可以为两片同样型号的存储器设置了不同的芯片地址,这样单片机就能通过芯片地址的不同对同一总线上的两块存储器分别进行读写操作了。存储器Nl、N2与电路的连接,采用插座方式。按放、拿取存储器电路时,需要使用开关“SW”将电源切断,保证断电操作。“复制”按键负责控制程序的运行。

连接好电路之后,接通电源,按动“复制”键,程序进入执行,单片机依次读取N2中的数据,并将数据写入到N1中,在这同时还将读写数据送入PO接口,通过PO接口的八只发光管显示出来。数据复制完成后,发光管熄灭。

程序设计

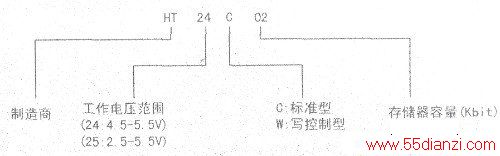

24Cxx是标准的低功耗可擦写可编程只读存储器,采用I2C总线进行数据读写,8脚形式的封装,02指可储存2Kbit(256字节)的二进制数据。

24Cxx芯片型号含义如下:

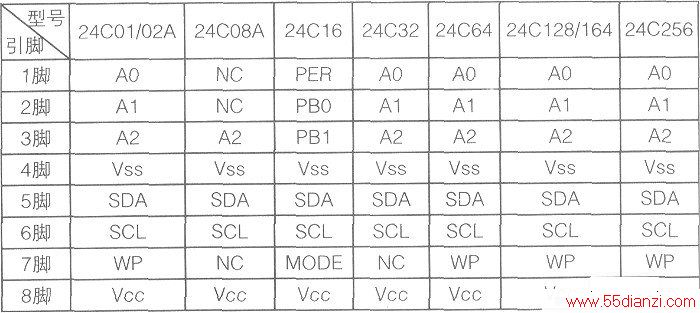

24C系列存储器引脚表见下表。

它的数据读取有三种模式:当前地址读、连续读取、随机读取。数据写入模式有随机写与页写两种。由于24CXX系列存储器随容量大小,硬件有较大差异,这就导致24C02、24C04、24C08等等各种容量的存储器之间的读写规则也有较大差异,这里仅对它们之间较为统一的随机单字节读取、单字节写入模式进行介绍。在这种模式下,可以由外部设备向储存器指定地址存入一个字节的数据或者从存储器特定地址读取一个字节的数据,即完成一次完整的读写操作。单字节随机读写模式下,24C04、24C08等芯片与24C02的读写方式总还有一些微小的差别,可参考芯片的相关资料介绍。

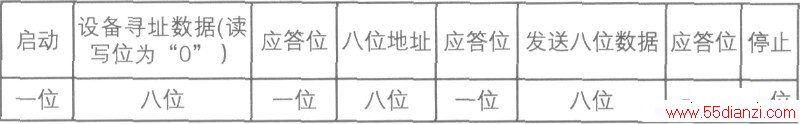

下表分别列出24C02在随机字节读、写方式下数据线(SDA)上传递的数据格式及完整的流程。

在与存储器通讯过程中,微处理器始终作为主机,所有的同步时钟都是理器发出。

启动信号由主机在第一个时钟周期发出。当主机访问存储器时,在时钟线(SCL)高电平期间,主机发出总线启动信号,使串行数据线(SDA)由高电平向低电平跳变。接到启动位后,挂接在同一条IIC总线上各个存储器进入待命状态,等待接收主机发出八位寻址数据。

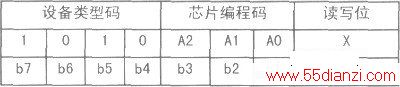

紧随启动位发出的八位设备寻址数据如下表所示,数据发送由最高位b7起,依次发送,每时钟周期发送一位,总长度为八个时钟周期。这八位设备寻址数据由b7、b6、b5、b4四位设备类型识别码、b3、b2、bl三位芯片编程码和一个读写位b0构成。

同一电路中所有芯片都可利用IIC总线进行相互间的讯息传递,为了对不同芯片进行区分,IIC总线协议为每种完成特定功能的芯片制定了各自的四位设备识别码,如显示驱动控制芯片的设备识别码为0111,数模、模数转换芯片的设备识别码为1001,而24C系列存储器之类的电可擦写可编程只读存储器电路的识别码统一指定为1010。

b3、b2、bl三位芯片编程码依次与24C02的A2、A1、AO三个引脚对对应,当引脚接+5V电源电压,对应位则为高电平“1”。如果引脚接地,则对应位为低电平“0”。在上述电路中,存储器N1的芯片编程地址为000,而N2的芯片地址则为001。由于有三位可编程地址,所以同一条IIC总线上可以挂接8块同样的24C02芯片,最大提供8×2Kbit=16Kbit的寻址空间。

最后一位读写(R/W)位用来指示数据传送方向。读写位为“0”低电平时,主机发出数据存入指定存储器地址空间,存储器作为接收方;读写位为“1”高电平时,主机读取存储器指定地址的数据,主机作为接收方。

每次八位数据接收发送完成后,数据接收的一方要发出一位应答信号,作为对数据发送方的回应,指示通讯成功,以便发送方为下一部作好准备。当主机作为发送方,发送完毕后,要释放数据线,进入待机。此时存储器要作出回应,由被寻址的存储器发出一位低电平信号,将数据线拉低,指示数据传输成功。当主机接收存储器数据时,回应信号则由主机发出。回应信号也由时钟同步,占一位时钟周期。

通讯完成后,在之后的一个时钟周期里,时钟线高电平期间由主机使数据线产生从低电平向高电平的跳变,以此作为停机信号,通知存储器停止数据传送。

在整个通讯过程中,数据线上高低电平的变化均须在时钟信号低电平期间完成,时钟高电平期间数据线电平保持稳定不变。之所以要这样,就是要将时钟高电平期间数据线上电压的变化保留用来指示总线通讯的启动和停止。

进行随机数据读取时,主机进行设备寻址,并发送寻址地址后,需要重新启动,将读写控制位设置变为“1”,以改变数据传送方向,使处理器成为数据接收一方。而数据写入时,存储器始终作为数据接收一方,读写控制位始终为“0”,所以不需重新启动,一次就可完成写入。

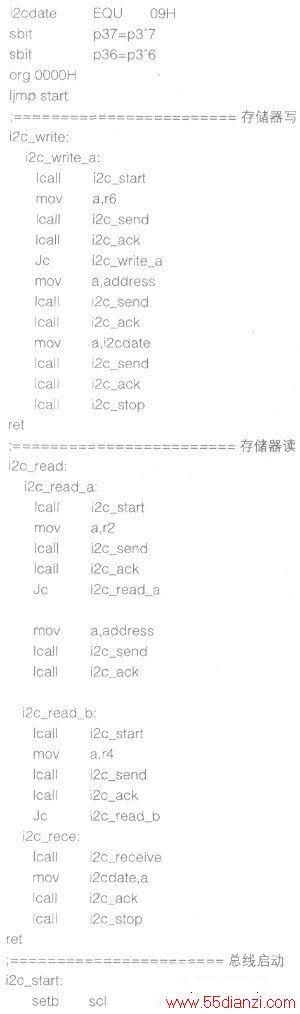

依据上述传输规范,可以写出24C02的数据拷贝汇编程序:

上一篇:PIC单片机调试器/编程器的制作