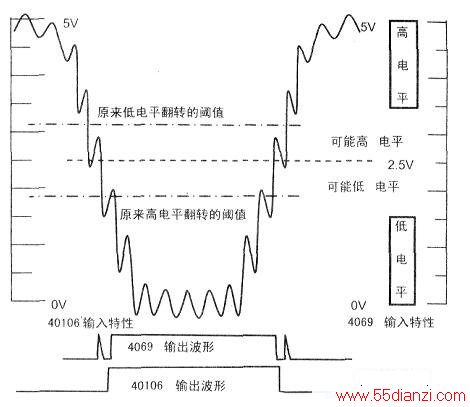

原来低电平要翻转,输入必须高于3.1V,从高电平翻转,输入必须低于1.9V。这样波形中的毛刺消除了,缓变的波形整形为很陡直的了。下图对照4O69和4O1O6的不同输入特性。

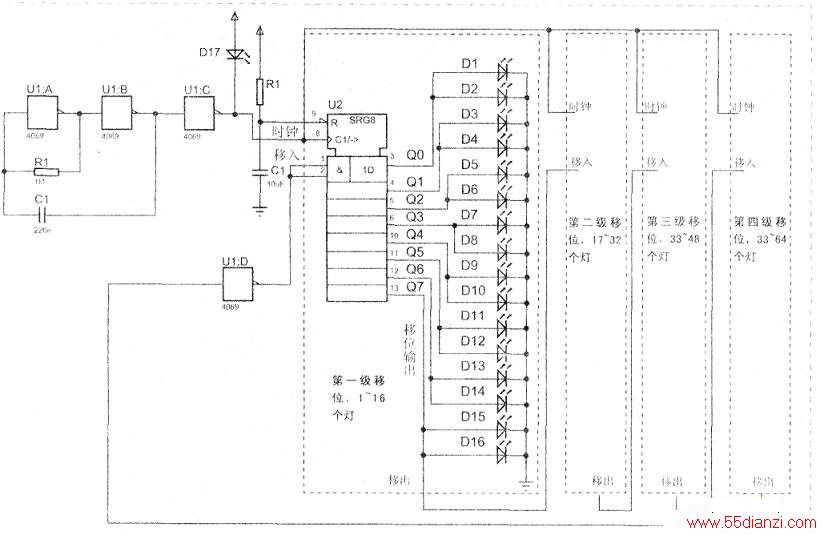

下图是一个设置在展窗框架周边的装饰灯.灯数逐步增多,全亮,逐步减少,全灭的走马灯设计.74LS164是一个8位串行输入并行输出的移位寄存器,开始全部输出端状态都为O,当数据输入第1脚和第2脚为1时,第8脚时钟由O变1,第3脚QO就变1,时钟再来一次第8脚由O变1,第3脚的数据1就移到第4脚Q1,Q2余次类推。当第13脚Q7为1时发出移出信号1,如此移位4×8=32位,64个灯全亮,当U5最后一位的移出信号=1,通过4O69第13脚反相,U1的12脚输出O,这时U2的1,2脚也就变O,时钟再来一次,U2的3,4,5脚QO,Q1,Q2……的状态为O11…….亮灯数从全亮。

逐步减少到全灭.图1O中的U14O69是CMOS六反相门,R1负反馈,第2脚输出通过R1负反馈到第1脚输入,如果输入1,经过反相输出应该为O,R1负反馈作用把1脚输入电平拉低,反之如果输入O,经过反相输出应该为1,R1负反馈作用把1脚输入电平拉高,所以第1脚输入端只能处在不高不低的中间电平,这时稍许有一点风吹草动.比中间电平略高或略低就会使第2脚变O或1,第二脚接第3脚。经过第二级反相,第4脚与第1脚同相,换言之,1脚为O,4脚就是O,1脚为1,4脚就为1.通过C1正反馈,第1脚的微小电压波动会得到加强。直到C1充放电结束。这样就构成CMOS多谐振荡器。控制R1C1时间常数,振荡频率约2Hz。

64灯串将每一秒移动2位,32秒从全灭逐步增加到全亮,32秒从全亮逐步减少到全灭。D17是指示灯。显示时钟节拍的。R2,C2使刚开机时U2清零。安装时,四个单元由四块印刷板组成,每个单元分别有自己的R,C清零。每个单元之间连接除了电源、地外,只需时钟、移入、移出三条线。

单元化机构保证LED连线整齐对称。

安装完毕检查无误,加电,居然只有D17闪烁,64灯亮暗杂乱。一点也不动。摸一摸,U2,U3。

U4,U5SN74LSl64很烫手。

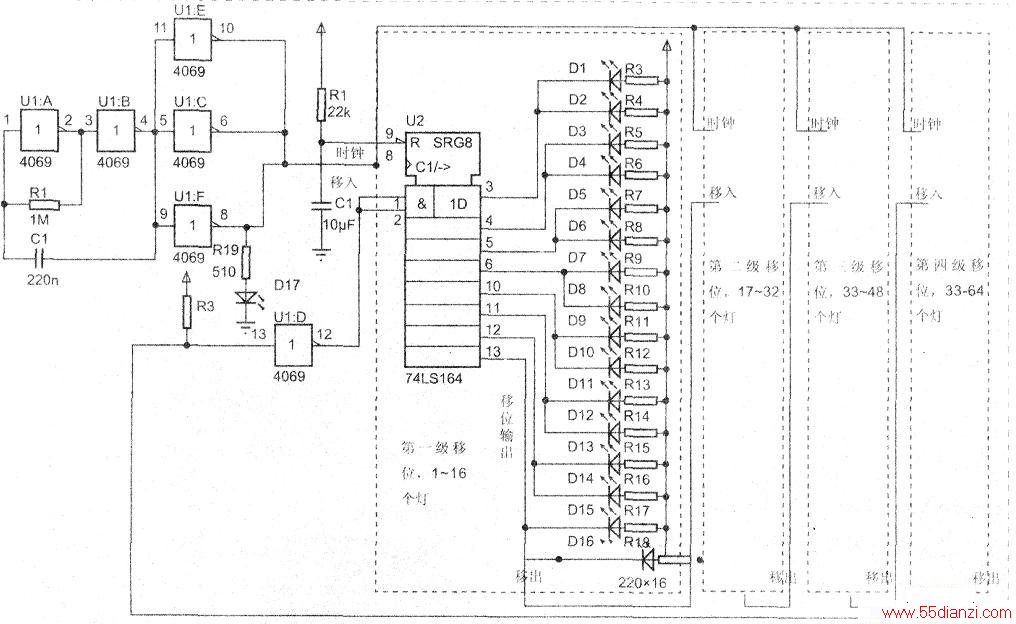

检查问题1:D17设计有问题,根据CMOS集成电路的输出模板模型,IC内阻8OOQ,LED灯导通时两端压2V。电流约(5—2)/8OO=3.75mA,IC输出高电平LED不通,输出为5V,IC输出低电平LED导通,被LED拉高到5—2=3V。根据2.2的模型,5/3显然不能与2.4/O.8匹配。先去掉D17,继续试验。

检查问题2:电路烫手。根据TTL集成电路的输出模型,用RH限流来点LED是不合理的,IC输出高电平时,LED亮,输出电流为:

[5V-1.4V(内部二极管)-2V(LED)]/12O(RH)=13.3mA8个灯全亮时,总电流为1O6mA,集成电路会很热。每个LED串1k电阻,灯暗了,IC发热小了。

检查问题3:64灯亮暗杂乱,时而能乱移动。

根据CMOS集成电路的输出模型,CMOS输出内阻8OOΩ根据2.2模型,每个TTL输入内阻1OkΩ。

共负载4个时钟输入端,并联电阻为2.5kΩ,去掉-个二极管D1的压降,分压得:1.O4V,处于图7中“可能低电平范围”,工作不稳定。受外界感应和集成电路温度影响大。将三个CMOS门并联,内阻降为266Ω,问题解决。

检查问题4:复位问题,TTL输入内阻1OkΩ,外接1MΩ和电容C2来形成开机低脉冲复位是不合理的。将R2改为22kΩ,C2改为1OμF,问题解决。由于连线长,U1D输入接417kΩ的上拉电阻R3,将第四级移位输出的电平从O~3.5V平移到O.2~5V,反相器工作比较稳定,修改后的64灯跑马灯设计如下图所示。

上一篇:模数转换电路工作原理