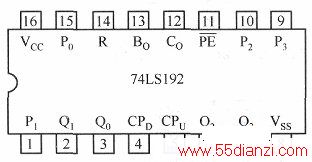

在TTL和COMS400系列中,十进制加减计数器的型号为74LS192和CD40192(以下均简称192,除非需要特殊说明时)。这两个型号的引脚完全相同,如果不考虑输入、输出电平问题则两者可以直接互换。192是一种带有预置的可以加、减计数(双时钟)的计数器。其引脚功能如下图所示。

通过加计数时钟(CPu)可以获得加计数功能;通过减计数时钟(CPD)可以获得减计数功能;利用预置端Po(20)、P1(21)、P2(22)、P3(23)和选通端PE实现预置数的设置;利用复位端R将输出数据清零。

192的输出有输出端Qo.Qi、Q2、Q3及进位位输出端Co和借位位输出端Bo。

192在作加计数时,从加计数时钟端CPu输入,这时的减计数时钟端CPD必须置1;同样,作减计数时,从减计数时钟端CPD输入,这时的加计数时钟端CPu必须置1;在预置数时,当预置数选通端PE为“0”时,预置数从预置端PO、Pl、P2、P3输入,送到输出端Qo、Q1、Q2、Q3。

进位位输出端Co在输出端Qo、Q1、Q2、Q3为1001(即十进制数“9”)并且同步加时钟脉冲的下降沿时为“0”;在加时钟脉冲的下一个上升沿到来时,进位位输出Co回到“1”,即给出一个进位位的上升沿,这个进位位的上升沿可以作为高位192的加计数时钟脉冲。同样,借位位输出端Bo在输出端Qo、Q1、Q2、Q3为0000(即十进制数“0”)并且减时钟脉冲的下降沿时为“O”;在减时钟脉冲的下一个上升沿到来时,借位位输出Bo回到“l”,即给出一个借位位的上升沿,这个借位位的上升沿可以作为高位192的减计数时钟脉冲。

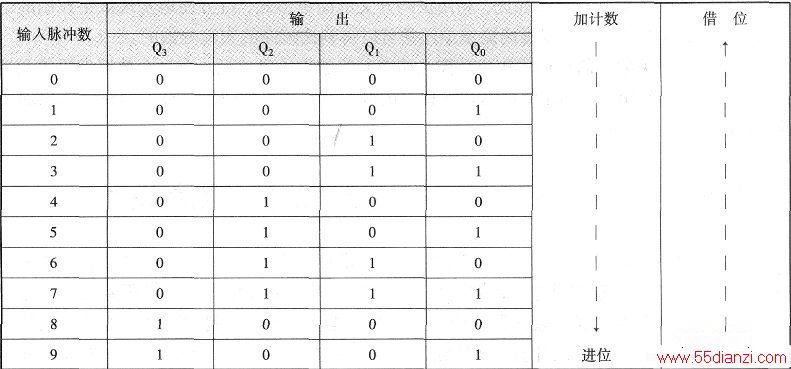

192的真值表如下表所示。

从表中可以看出,在加计数过程中,随着输入的时钟脉冲数的增加(0~9),输出从0000增加到1001,当输出为1001后进位位由高电平转变为低电平,随着加计数时钟脉冲的继续增加,输出由1001变为0000,同时进位位由低电位转变为高电位,给出进位脉冲的上升沿;同理,在减计数过程中,随着输入的时钟脉冲数的增加(0~9),输出从1001减少到0000,当输出为0000后借位位由高电平转变为低电平,随着加计数时钟脉冲的继续增加,输出由0000变为1001,同时借位位由低电位转变为高电位,给出借位脉冲的上升沿。

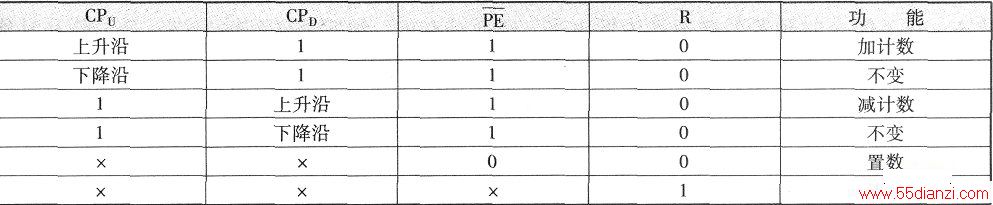

192的功能表如下表所示。

从表中可以看到,当清零端R为高电平“l”时,不管其他输入端如何,输出端均被清零,为0000;当PE端为“0”时192为预置数状态,无论加计数时钟和减计数时钟的状态如何,输出均与选通端相同,即与加计数时钟和减计数时钟的状态无关。只有在清零端为“0”、选通端PE为“1”时,计数时钟脉冲才会有效,但是需要注意的是,加计数状态时,减计数时钟必须为“l”;而减计数状态时,加计数时钟必须为“1”。

选通端为“1”时选通端不起作用,输出端仅受加、减计数时钟的控制。

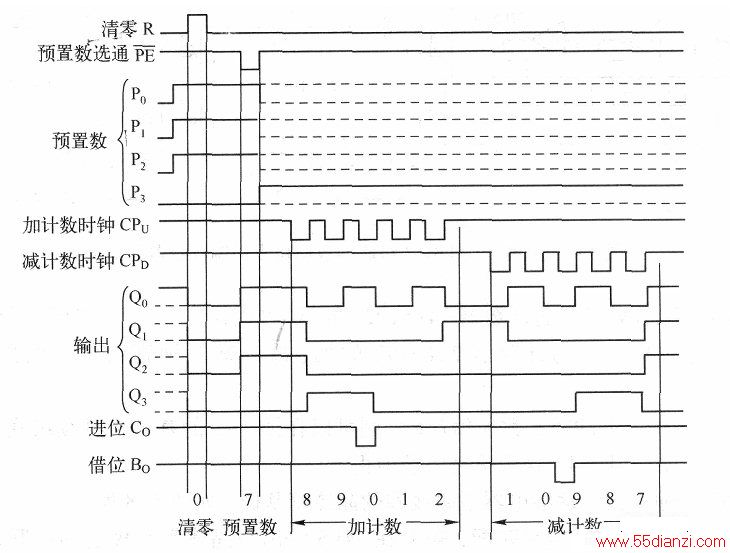

通过上表的描述,可以得到192的主要波形图,如下图所示。

通过上表和上图的描述,就可以知道怎样使192正常运行了。

上一篇:DAC在函数发生器里的速度