初学者可能会遇到这样的问题,在Run As Nios II Hardware下方,看到Run As Nios II ModelSim就觉得很奇怪,Nios II明明是嵌入式系統,怎么能用ModelSim仿真呢?

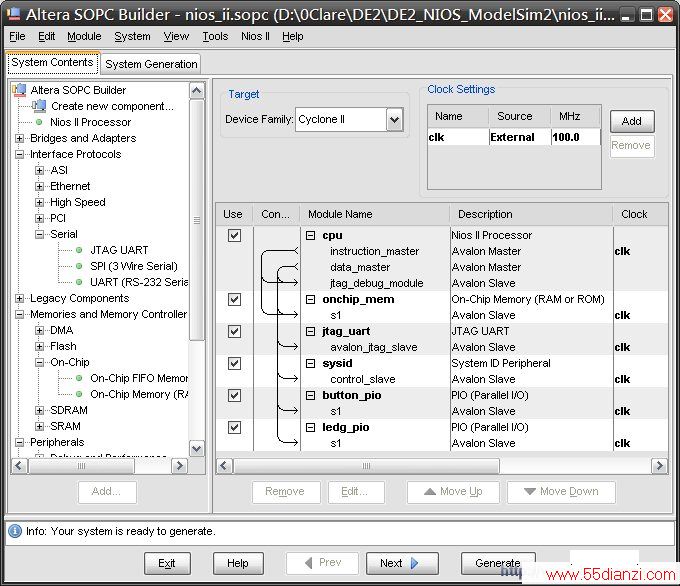

使用環境:QUARTus II 7.2 SP3 + Nios II EDS 7.2 SP3 + ModelSim-ALTEra 6.1g + DE2(Cyclone II EP2C35F627C6)

用ModelSim对数字系统作仿真,这个大家可能都很熟悉。Nios II虽然是个嵌入式系统,但毕竟基于FPGA技术,所以比ARM这类hardcore多了使用ModelSim仿真的方式。这也是Altera四大天王(Quartus II、Nios II EDS、ModelSim-Altera、DSP Builder)中的三大天王首次同台演出。

Altera在文件中,有谈到如何用ModelSim-Altera对Nios II作仿真,不过一如以往,Altera的文件要在DE2能动,还是得做不少修改。

Quartus II与SOPC Builder部分

Step 1:

文件中的那个系统并不适合DE2,用了一定不能动,所以就自己建立一个最简单的Nios II系统。为了要简单,就先使用onChip memory与LEDg与button就好,其他IP都先别用,以减少失败的变因。

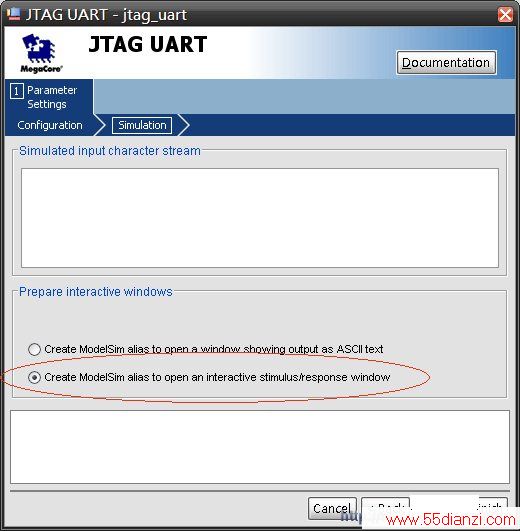

Step 2:

JTAG UART设定

使用ModelSim-Altera仿真后,对于C的printf()要怎么显示呢?这要对JTAG UART做设定。

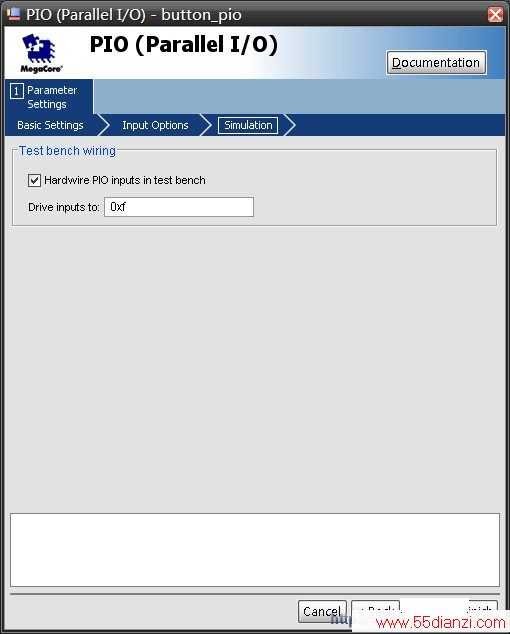

Step 3:

Button本来是在runtime由user去决定,若你想在testbench就模拟user的按键,可在此设定,此步骤并非必须,只是demo可藉由此方式设定PIO的初始值。

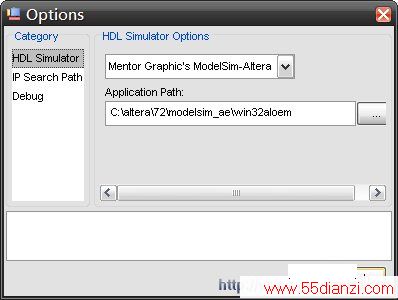

Step 4:

在SOPC Builder设定ModelSim-Altera路径

Tools -> Options -> Category:HDL Simulator

Step 5:

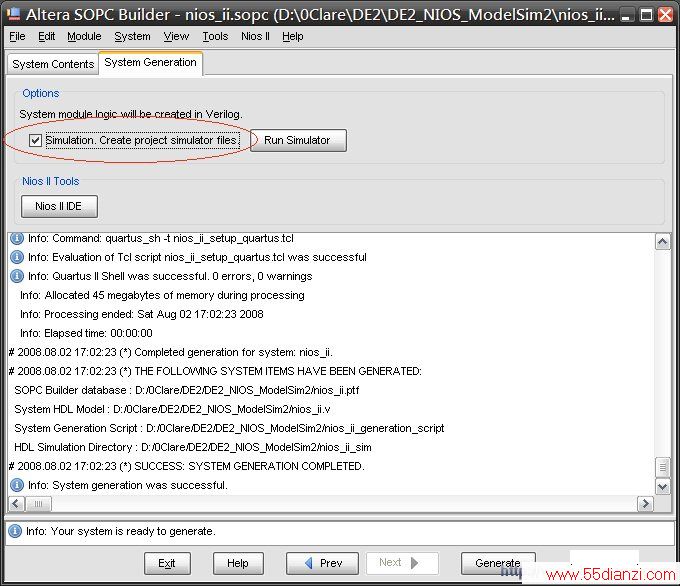

记得要将『Simulation. Create project simulator files』打勾。

Step 6:

DE2_NIOS_ModelSim2.v / Verilog

1 /*

2 (C) OOMusou 2008 http://oomusou.cnblogs.com

3

4 Filename : DE2_NIOS_ModelSim2.v

5 Compiler : Quartus II 7.2 SP3

6 Description : Demo how to simulate Nios II by ModelSim-Altera

7 Release : 08/02/2008 1.0

8 */

9

10 module DE2_NIOS_ModelSim2 (

11 input CLOCK_50,

12 input [3:0] KEY,

13 output [8:0] LEDG

14 );

15

16 wire CPU_CLK;

17 wire CPU_RESET;

18

19 Reset_Delay delay1 (

20 .iRST(KEY[0]),

21 .ICLK(CLOCK_50),

22 .oRESET(CPU_RESET)

23 );

24

25 SDRAM_PLL PLL1 (

26 .inclk0(CLOCK_50),

27 .c1(CPU_CLK)

28 );

29

30 nios_ii u0 (

31 .clk(CPU_CLK),

32 .reset_n(CPU_RESET),

33 .in_port_to_the_button_pio(KEY),

34 .out_port_from_the_ledg_pio(LEDG)

35 );

36

37 endmodule

25行

SDRAM_PLL PLL1 (

.inclk0(CLOCK_50),

.c1(CPU_CLK)

);

别被SDRAM_PLL吓到了,只是借用这个PLL产生100 MHz的clock给Nios II用,你也可以自己重新产生一个100 Mhz的clock而不用SDRAM_PLL。

Quartus II与SOPC Builder部分已经完成,编译后可烧进DE2。

(

www.55dianzi.com

Nios II EDS部分

Step 1:

建立Hello World project

hello_world.c / C

1 #include <stdio.h>

2 #include "system.h"

3 #include "aLTEra_avalon_pio_regs.h"

4

5 int main() {

6 int i;

7 printf("Hello from Nios II!\n");

8

9 for(i = 0; i < 256; i++)

10 IOWR_ALTERA_AVALON_PIO_DATA(LEDG_PIO_BASE, i);

11

12 return 0;

13 }

LEDG_PIO_BASE這個巨集跟文件的不一樣,因為在SOPC Builder中,我們已經使用了不同的名稱。

Step 2:

修改System Library设定

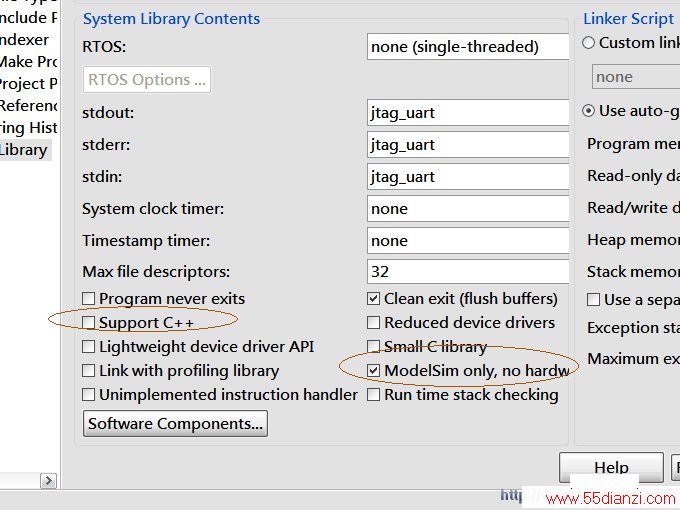

由于我们使用的onChip memory只有40K,正常的Nios II是无法执行的,所以必须做些设定,让code size变小。在Altera原厂文件并没有这一步,因为它用的是SDRAM够大,根本不用考虑code size的问题。

选择不支援C++会让code size小一点,另外要勾选ModelSim only, no hardware。

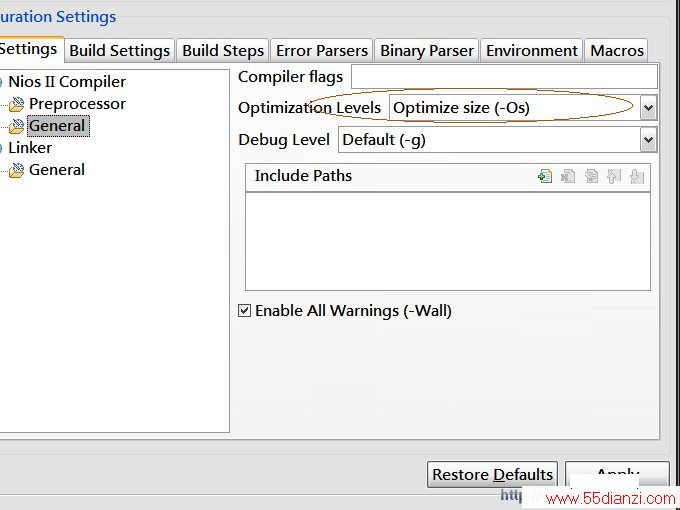

设定让gCC编译出的code size小一点,若你对code size最佳化有兴趣,建议参考。

Step 3:

编译Hello World且Run As Nios II ModelSim。

Nios II EDS部分已经完成,接着会出现ModelSim-Altera。

(

www.55dianzi.com

ModelSim-ALTEra部分

Step 1:

编译Verilog

QUARTus II已经产生好ModelSim的macro,你只要打s就可重新编译,这是最危险的时刻,若会失败都是出在这个时候,我之前曾经使用友晶的Nios II Reference Design来做仿真,但有些module无法编译成功,目前原因还不明。若成功编译,会有以下的结果:

# Reading C:/altera/72/modelsim_ae/tcl/vsim/pref.tcl

# Reading D:/0Clare/DE2/DE2_NIOS_ModelSim2/nios_ii_sim/modelsim.tcl

# c:/altera/72/quartus//sopc_builder

# c:/altera/72/quartus//bin/perl

# Sopc_Builder Directory: c:/altera/72/quartus//sopc_builder

# @@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@

# @@

# @@ setup_sim.do

# @@

# @@ Defined aliases:

# @@

# @@ s -- Load all design (HDL) files.

# @@ re-vlog/re-vcom and re-vsim the design.

# @@

# @@ c -- Re-compile memory contents.

# @@ Builds C- and assembly-language programs

# @@ (and associated simulation data-files

# @@ such as UART simulation strings) for

# @@ refreshing memory contents.

# @@ Does NOT re-generate hardware (HDL) files

本文关键字:暂无联系方式电脑-单片机-自动控制,电子学习 - 基础知识 - 电脑-单片机-自动控制