дVerilogʱ����Ȼÿ��module��������ModelSim��QUARTus II�Դ���simulator�����������Ľ�ÿ��module�ϲ�ʱ��һЩ����Ԥ�ڵ�“run-time”������ܲ�һһ���֣���ʱ�ÿ�SignalTap II����ædebug��

ʹ�û�����Quartus II 8.0 + DE2-70 (Cyclone II EP2C70F896C6N)

ʵ��ʹ��SignalTap IIʱ���ᷢ����Щreg��wire���Թ۲죬��Щ�����۲죬����������������reg��wire�۲췽����

�۲�reg

SSignalTapII_register_not_preserve.v / Verilog

- module SignalTapII_register_not_preserve (

- input ICLK,

- input iRST_N

- );

- reg [3:0] cnt;

- always@(posedge iCLK, negedge iRST_N) begin

- if (!iRST_N)

- cnt <= 4'h0;

- else

- cnt <= cnt + 4'h1;

- end

- endmodule

���Ǹ��ܼļ��������ҹ�����cnt����output��������SignalTap IIȥ�۲�cnt���reg��ֵ��

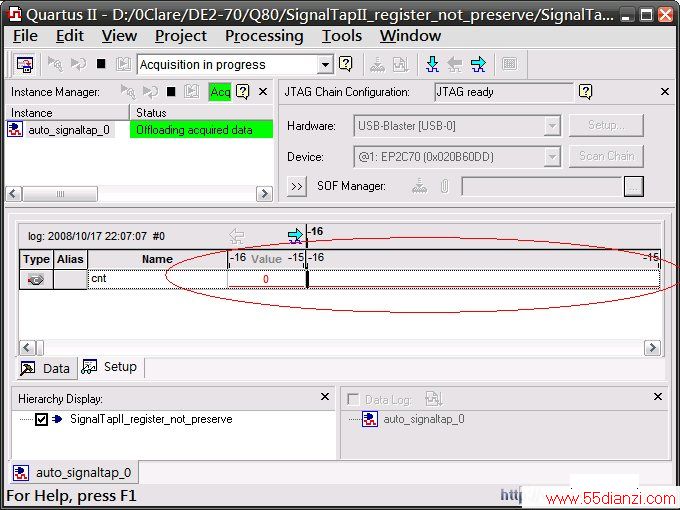

cnt����0����Ȼ����������ʾSignalTap II��capture cnt���reg��ֵ��Ϊʲô��������?

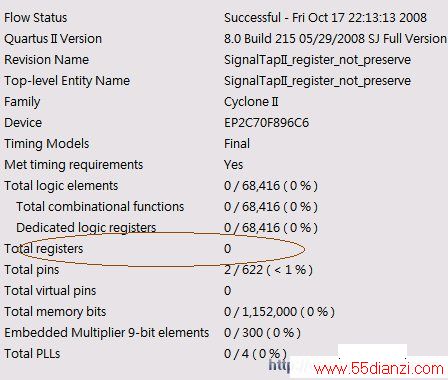

�����ǽ�SignalTap II�õ���������Quartus II���룬�۲���compilation report����ʾregisterΪ0��

�۲�RTL Viewer�ĺϳɽ�������û��register!!

��֤����һ�����飬Quartus II�ںϳ�ʱ������cnt��û����Ҫoutput�����Զ���ѻ����ϳ�cnt������SignalTap II���۲�reg��������ʱΪ��debug���㣬���Ǿ�����۲�����reg���а취��Quartus II��ʱ��Ҫ������ѻ���?

ʹ��Synthesis Attribute������ѻ�

SignalTapII_register_preserve.v / Verilog

- module SignalTapII_register_preserve (

- input iCLK,

- input iRST_N

- )

- reg [3:0] cnt /*synthesis noprune*/;

- always@(posedge iCLK, negedge iRST_N) begin

- if (!iRST_N)

- cnt <= 4'h0;

- else

- cnt <= cnt + 4'h1;

- end

- endmodule

6��

reg [3:0] cnt /*synthesis noprune*/;

����/*synthesis noprune*/���synthesis attribute��ָʾQuartus II��Ҫ��cnt����ѻ���������register�Թ�SignalTap II�۲죬ע�����д�ڷֺ�ǰ�棬��������д�ڷֺź��档

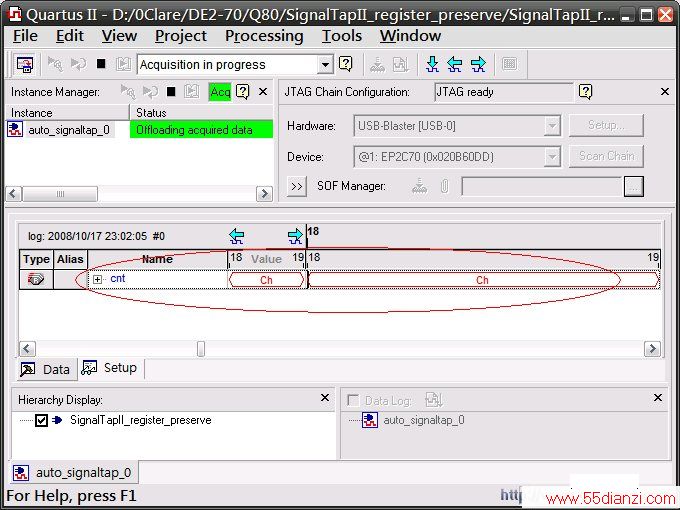

�����SignalTap II����˳���Ĺ۲쵽cnt��ֵ!!�ص��Dz����top module��interface��ֻ�����۲��reg����synthesis attribute���ɡ�

Quartus IIҲ֧ԮVerilog 2001���Z��

- module SignalTapII_register_preserve (

- input iCLK,

- input iRST_N

- );

- // Verilog 2001

- //(*noprune*) reg [3:0] cnt;

- always@(posedge iCLK, negedge iRST_N) begin

- if (!iRST_N)

- cnt <= 4'h0;

- else

- cnt <= cnt + 4'h1;

- end

- endmodule

7��

(*noprune*) reg [3:0] cnt;

����Verilog 2001�����Quartus II 8.0Ҳ�ܿ��ö���

��ϣ������module��reg��������ѻ����ɽ�synthesis attribute����module��

- module SignalTapII_register_preserve (

- input iCLK,

- input iRST_N

- ) /*synthesis noprune*/;

- reg [3:0] cnt;

- always@(posedge iCLK, negedge iRST_N) begin

- if (!iRST_N)

- cnt <= 4'h0;

- else

- cnt <= cnt + 4'h1;

- end

- endmodule

1��

module SignalTapII_register_preserve (

input iCLK,

input iRST_N

//);

) /*synthesis noprune*/;

��/*synthesis noprune*/����module����������module��reg��������ѻ���������һһָ����

����һ����reg��ص�Synthesis Attribute��/*synthesis preserve*/

��reg��ص�attribute������/*synthesis noprune*/���ã�����һ��/*synthesis preserve*/���ã����ߵIJ������ڣ�

/*synthesis noprune*/����Quartus II�Ż���ûoutput��reg��

/*synthesis preserve*/����Quartus II��reg�Ż�Ϊ���������ߺϲ��ظ���reg��

Ҳ����ʹ��Verilog 2001��д��

//(*preserve*) reg [3:0] cnt;

��������module���

���Ĺؼ��֣�������ϵ��ʽ����-��Ƭ��-�Զ�����������ѧϰ - ����֪ʶ - ����-��Ƭ��-�Զ�����