1 引言

随着IC工艺的提高,从几百兆赫到几千兆赫的处理器已经非常普及,以往的低速PCB设计方法已完全不能满足日益增长信息化发展的需要.利用EDA工具分析解决高速设计所而临的问题是一种有效办法。在设计的过程中,由EDA工具对输入器件模型数据进行分析,将结果直接反给设计者,设计者根据反馈信息对设计进行修改完善.从而缩短了开发周期,避免了人力、财力的浪费。

2 系统组成

本试验平台采用Motorola 公司的Dragonball系列芯片中的MC9328MX1,其CPU时钟速度200MHz;SDRAM采用了SUMSUNG公司的同步 K4S281632E,时钟速度100MHz以上。由于地址总线和数据总线的布线密度比较大,速度较高,系统对信号完整性要求较高,因此采用MENTOR 公司的PADS2004设计软件,它将原理图设计、PCB Layout和高速仿真分析集成于一体,可以解决在PCB设计中存在的信号完整性、串扰等问题,大大提高了设计成功率。

系统没计中最关键走线的是SDRAM与MC9328MX1之间的连接走线,它们的信号完整性直接影响着系统能否正常工作。PCB设计中,采用 PADS2004软件的高速仿真工具HyperLynx进行仿真,HyperLynx包括LineSim和BoardSim 两部分,其中LineSim是布线前仿真工具,而BoardSim是布线后仿真工具。仿真模型采用IBIS模型,IBIS模型采用I/V和V/T表的形式来描述数字集成电路I/O单元和引脚的特性。由于IBIS模型无需描述I/O单元的内部设计和晶体管制造参数,因而受到半导体厂商的欢迎和支持,现在各主要数字集成电路制造商都能在提供芯片的同时提供相应的IBIS模型。

3 系统设计

3.1 电源分配

高速系统板设计中电源层的网络分配很重要。在PCB布线方面,PCB板首先要考虑电源的完整性,它直接影响最终PCB板的信号完整性。很多情况下,影响信号畸变的主要原因是电源系统,例如去耦电容设计不好,地层设计不合理,电流分配不均匀,地弹噪声太大,回路影响很严重等。

由于电源层是通过整个金属层来分配电源,其电源阻抗很小,所以电源噪声也比总线式小得多,因此设计时将电源单独作为一层。

为了消除电源噪声,在电路板的电源输入上放置一个47uF电容,用来消除低频噪声。在板子上的每个有源器件的电源引脚和接地引脚上放置一个0.1uF高频滤波电容来滤除线路高频噪声。滤波电容应尽量接近电源引脚,使电源引脚到滤波电容的走线最短来取得最好的滤波效果。

3.2 时钟设计

时钟设计在PCB设计中是很重要的一部分,通过规划时钟线,使得时钟线的连线远离其它的信号线,时钟在跟地层相邻的信号层上走,走线尽量在一层走,不要穿越多层。时钟线和其它数据、地址线之间的距离应该满足3W原则(绕线的间距要两倍于线宽)。时钟连线尽量短,并且加上地线保护。为了保证时钟信号的完整性,时钟的输出串接一个33欧姆左右的端接电阻。

3.3 关键信号与非关键信号

在仿真分析前,先对系统中的信号进行划分,划分为关键信号与非关键信号。划分的原则主要是根据器件驱动沿速率快慢、工作频率的高低与信号线长度等条件进行划分,当然还应依实际的设计而定。

在本系统中,关键信号有:时钟信号;CPU与SDRAM、CPU与FLASH等 存储 器的数据线、地址线以及读写等控制信号线。其中最关键的是SDRAM与 MC9328MX1之间的连接走线,它们的信号完整性好坏直接影响着MC9328MX1能否将数据正确存取于SDRAM 中。

4 仿真分析与结果

4.1 LineSim仿真

在原理图完成之后即可进行布线前信号完整性仿真,在这里使用HyperLynx的布局前分析工具LineSim完成布线前仿真。LineSim用在布线设计以前约束布线和各层的参数、设置时钟的布线拓扑结构、选择元器件的速率、诊断并避免信号完整性、电磁辐射等问题。

LineSim进行布线前仿真是很方便的,将厂商提供的IBIS模型添加到相应的模型库中,在LineSim原理图中将驱动端,接受端以及它们之间的连线方式设置好,就可以进行仿真了。LineSim还提供了对仿真结果一些建议,如连线的拓扑结构、连线的长度、端接电阻和电容的数值是否匹配等。

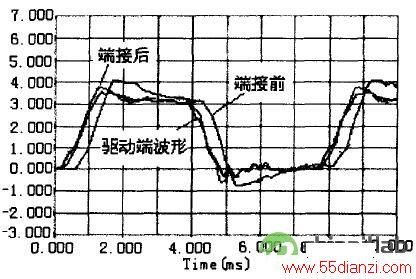

通过在布线之前信号完整性分析对布局进行指导,对逻辑器件的类型进行选择,决定哪些信号需要端接,以及采用何种端接方法及端接电阻的阻值大小。图1是在工作频率为100 MHz时数据线D0添加33欧姆的并联电阻端接前与端接后信号完整性分析的不同结果,可以看出在端接后明显消除了上冲与下冲,且振荡也大幅度地减小了

图1 数据线D0仿真波形

4.2 BoardSim仿真

在布线前信号完整性仿真指导下完成布局布线之后,还可能存在一些信号完整性问题,如相邻线网之间的串扰、EMC等,所以需要进行布线后的信号完整性仿真,对完成布线后的设计进行进一步的分析。在这里使用HyperLynx的布局后分析工具BoardSim完成信号完整性分析。BoardSim用于布线以后快速地分析设计中的信号完整性、电磁兼容性和串扰问题,生成串扰强度报告,区分并解决串扰问题。

对于某一网络,像LineSim一样,BoardSim可以进行单独仿真,BoardSim还可以进行串扰仿真,相互耦合干扰的网络仿真结束后显示为白色。通过进行串扰仿真,可以很方便的找出相互干扰的网络,通过改变网络的间距或者是减小介质层厚度可以减小串扰。

对于整个PCB板,BoardSim可以进行快速仿真和详细仿真,快速仿真,可以高效地分析PCB板,查找信号完整性和EMC等问题;详细仿真提供了更具体的报告信息,针对一个网络上的每个接收端IC的PIN、详细的过冲、最小/最大IC Pin的延迟和极限域值等。仿真结果以文本型式输出,这是一个很完整的分析报告,可以通过关键字“find warning”和“find warning(severe)”来找警告位置,该位置就是可能会出现信号完整性或者是EMC问题的地方。

根据布线后信号完整性仿真的仿真结果,通过改变端接方式与具体阻值即在驱动端添加不同阻值的串联端接、在负载端添加不同阻值的并联端接、调整端接的位置、修改走线的拓扑结构、调整板层间的介质厚度等方法进行反复的修改与仿真验证,将各种信号完整性问题限制在可接受的范围之内。

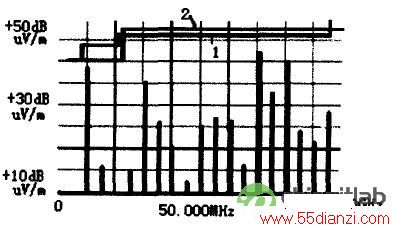

图2为数据线D0产生的电磁辐射仿真图,图中曲线1与曲线2分别代表欧洲以及美国的规定辐射容限,垂直条为数据线D0在不同频率下产生的辐射分贝值,从图中可以看出,数据线Do产生的辐射均低于欧洲和美国所规定的辐射容限,符合要求。

4.3 实际结果分析

PCB制版后,为了 测试 PCB的性能和信号完整性,将MC9328MX1和SDRAM的运行速度设置在最高频率100MHz, 测试 其时钟线、地址线和数据线的波形,图3为数据线D0在最高频率100MHz下的波形图。比较图1可以看出,当SDRAM运行于100MHz时数据线的波形较好,证明仿真的结果是可信的。由此,系统平台中MC9328MX1与SDRAM之间的数据传输可以达到其传输的最高性能。从而验证了HyperLynx仿真软件对信号完整性和 EMC分析的正确性。

5 结束语

随着数字器件切换速度的逐步提高,信号完整性、串扰EMC分析对于设计成功的高速PCB设计而言越来越重要。在设计早期和设计期间进行信号完整性,串绕和 EMC分析问题有利于为PCB布线产生约束条件;避免昂贵的PCB返工,节省了大量的时间。在本设计中,借助基于IBIS模型和HyperLynx仿真工具进行信号完整性仿真分析,解决了许多信号完整性问题,避免了因信号完整性问题可能带来的重复制板,缩短了设计周期。

本文关键字:暂无联系方式制版技术,电子制作 - 制版技术