本文设计了一种模拟除法器,在分析讨论其工作原理的基础上,采用CSMC0.5umCMOS工艺,对电路进行了Cadence SpeCTRe 模拟仿真,仿真结果验证了理论分析。

1 电路的设计与分析

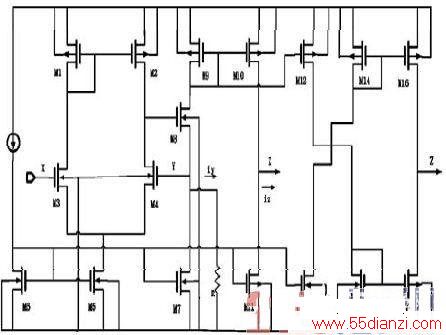

图1 CCII 电路结构

模拟除法器由单电源+5V供电,主要由两部分电路构成。第一部分为第二代电流传输器CCII,图1 为CMOS CII电路。晶体管M3和M4 组成一个差分放大器,放大器的输出经过晶体管M8 传输到Y端,而晶体管M1 和M2构成的电流镜则是差分放大器的有源负载。假设晶体管M1 与M2、M3 与M4、M9与M10 是匹配的,晶体管M5、M6、M7 和M11 组成偏置电流镜,分别为三个支路提供偏置电流,且I7=I11。晶体管M1、M2 组成的电流镜迫使晶体管M3 和M4的漏源电流相等,于是有Vgs3=Vgs4,又晶体管M3 与M4 为源极耦合对,所以晶体管M3 与M4的栅压相等,即Vx=Vy。晶体管M8作为源极跟随器,在Y 端提供了低的输出阻抗。如果Vy》0,且R是Y 端电阻,则从Y 端流出的电流为iy=Vy/R,晶体管M8 的漏极电流为(I7+iy),该电流通过电流镜M9与M10 的作用复制到Z端。因为I11=I7,所以Z端流出电流与Y 端的电流相等,即iz=iy。

晶体管M12-M17组成交叉耦合电流镜将电流(I7+iy)复制到Z端口,由于电流I16 跟随电流I7 变化,因此电流iz 流动为反方向,即iz=-iy 。

由此,可以看出CCII 电路可以实现:

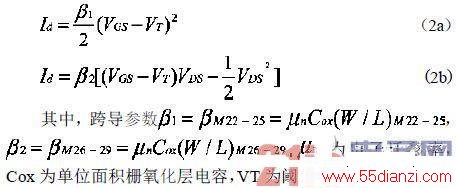

第二部分电压电流转换电路如图2 所示,晶体管M20、M21 提供恒定且相等的电流源。晶体管M22-M25 工作在饱和区,M26-M29 工作在线性区。忽略体效应,则漏电流Id:

图2 电压电流转换电路

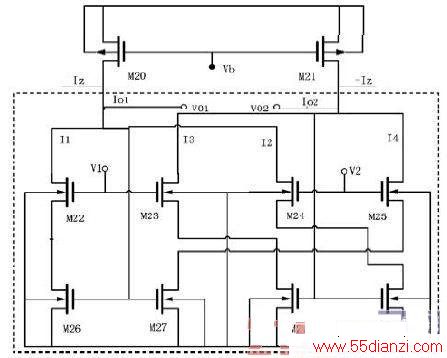

图2 中虚线部分电路可分为四个支路,由晶体管对(M22,M26)(M23,M28)(M24,M29)(M25,M27)构成。电压V1、V2为输入信号。根据方程式(2a)和(2b),我们可以得到四个支路的电流与电压的关系式:

将等式(3)-(6)按照泰勒级数展开,如(7)式所示,将其在(0,0)点二阶展开:

并对其路径积分之后,总的差分输出电流:

于是有,定义差分输入V=V1-V2

而差分输入电流:

由方程式(9)、(10)、(11)和(1)有

2 电路仿真结果

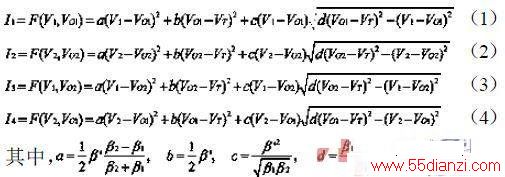

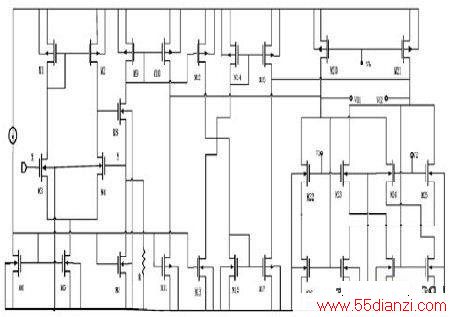

模拟除法器的整体电路如图3 所示:

图3 除法器的整体电路图

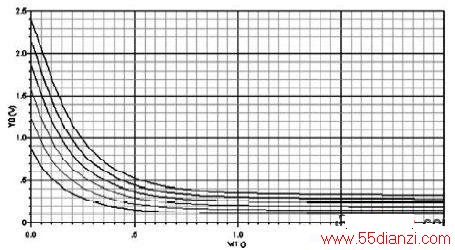

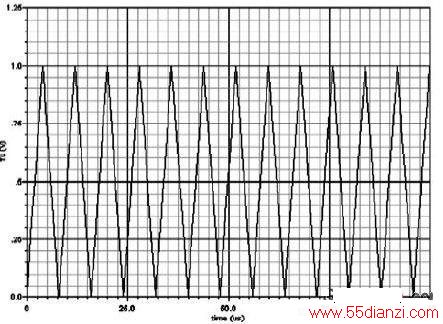

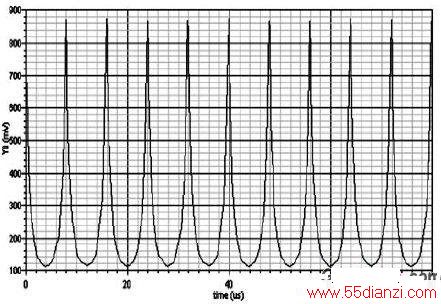

整个电路采用CSMC的0.5um CMOS工艺设计,经过CadenceSpeCTRe仿真,结果表明,在单电源+5V供电情况下,输入V从0V到2V变化,对输入Vx从1V-2V 进行DC扫描,扫描步长为200mV,所得直流特性曲线如图4 所示;当输入Vx 为1V 时,输出Vo 与V 的关系,为Vo∝1/V ,图5(a)为输入V为频率20KHz 的三角波,图5(b)中的曲线为输出电压Vo 。图6为除法器的频率响应(Vx=2V, V=0.2V),它的-3dB 带宽大约是60MHz。总体电路的静态电流不到0.9mA,静态功耗小于4.5mW。

图4 直流传输特性曲线图

图5(a) V 端输入信号

图5(b) Vo 输出瞬态响应

图6 频率特性

3 结语

本文设计了一个模拟除法器,很好地实现了两个电压之间的相除,具有较好的频率特性、较低的静态功耗等特点。

本文关键字:暂无联系方式工艺技术,电子知识资料 - 工艺技术

上一篇:IGBT模块的静电对策与门极保护