图2 AD7656并行接口读操作数据流

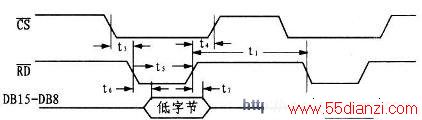

如果只有8bit总线被使用,那么AD7656的接口将以字节模式(W/B=I)操作,这种操作下的转换结果将通过2次读操作来访问,每次读操作通过 DB15-DB8来访问1个8bit的数据,如图3所示。其中,tCONV为转换时间3μS,内部时钟tQUIET为总线的废弃时间到下1个转换开始之间所必需的最小等待时间,最小值为400ns;t1为读操作时的最小时间20ns;t2为BUSY信号到RD信号之间的延迟时间(ns);t3为CS到RD 之间的建立时间(ns);t4为CS到RD之间的保持时间(ns);t5为RD的脉冲宽度,最小值为30ns;t6为RD下降沿后的数据访问时间,最大值为30ns;t7为RD上升沿之后的总线废弃时间,最小值为15ns,最大值为25ns。

图3 AD7656并行接口一字节模式下的读操作

3.2系统组成

图4所示是AD7656在并行接口状态下的外围电路连接。其中的DVcc和AVcc分别是数字电压端和模拟电压端,它们在接入前要经过1个去耦电路,如图4所示,每个供电电压输入引脚都要连接1个去耦电路,该电路由1只10μF和1只100nF的电容器组成。VDD、Vss和VDRIVE同样要连接去耦电路。

图4 基于AD7656的并行模式数据采集系统

AD7656的输出接到FPGA中进行数字信号的滤波处理,然后再送入数字信号处理器(DSP)进行处理。用FPGA控制引脚CONVSTA/B/C、 RD和CS的状态,可以用编程的方法或硬件连接的方式来实现。系统中的FPGA是ALTERA公司的EP1K30,DSP选用ADI公司的TS101S。此系统的外围电路比较简单,比较容易实现,具有真正的高速、高性能数字信号采集功能。

3.3应用程序举例

4、注意事项

在绘制PCB版图时,要注意将AD7656的模拟和数字部分分开布局,并把它们放在板上的特定区域,这样可以使地层比较容易分开,使用起来比较方便。数字地层和模拟地层应该在板上的某一处连接到一起,可以用0Ω电阻器,也可以使用磁珠或直接用焊锡连接。建议在布线的时候不要将数据线布在该器件的下方,因为这样做会使信号和噪声混在一起。电源线应该尽量粗一些,这样可以尽量减小电源线的脉冲干扰。去耦电容器应尽量地靠近器件,之间的连线要尽量短以减小感抗。电路的性能除了受核心ADC的影响外,还受到各种外围辅助电路性能的影响。

5、结束语

本文介绍了采用先进的工业CMOS(iCMOS)工艺制造的AD7656型模,数转换器,并将它应用在数字采集系统中。多通道模/数转换器同步采样技术提高了数字信号处理的速度和精度。AD7656的外围电路配置简单,应用领域也会越来越广泛。

本文关键字:暂无联系方式元器件特点及应用,元器件介绍 - 元器件特点及应用