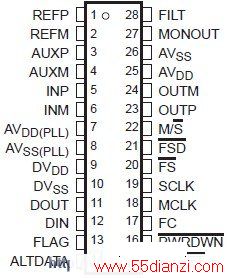

图1 TLC320AD50C引脚图

TLC320AD50C的特点如下:

(1)器件中的ADC为64倍过采样,DAC为256倍过采样(内部);

(2)带有内建抗混叠滤波器和sinx/x补偿;

(3)可配置成主机或从机方式,一个串行接口可支持3个从设备和DSP进行通讯。

TLC320AD50C中的可选项和电路配置可以通过串行口进行编程,具体可编程项有:复位,掉电,通信协议,串行时钟率,信号采样率,增益控制,测试模式等。

TLC320AD50C有7个控制寄存器。其中,控制寄存器1:软件复位以及DAC的16位或15+1位模式选择;控制寄存器2:ADC的16位或15+1位模式选择;控制寄存器4:选择输入和输出放大器的增益;通过选择N确定采样速率fs;选择PLL,如果选择PL(D7=0),则fs=MCLK/(128N),否则(D7=1),fs=MCLK/(512N)。其中,N=1-8。

其中主要4个寄存器功能如图2。由于寄存器4可修改采样频率,所以可能经常被修改,二次通讯很多涉及到它。

图2 TLC320AD50C四个寄存器功能汇总

TLC320AD50C的通信协议

TLC320AD50C的通信有两种格式:一次通信格式和二次通信格式。

一次通信格式的16位都用来传输数据。DAC的数据长度由寄存器1的D0位决定。启动和复用时,缺省值为15+1位模式,最后一位要求二次通信。如果工作在16位传输模式,则必须由FC产生二次通信请求。

二次通信格式则用来初始化和修改TLC320AD50C内部寄存器的值。在二次通信中可以通过向DIN写数据来初始化。格式如下:

系统复位后,必须通过DSP的DX口向TLC320AD50C的DIN写数据,如果采用一片TLC320AD50C,只需初始化其寄存器1、寄存器2和寄存器4。

系统复位后,必须通过DSP的DX口向TLC320AD50C的DIN写数据,如果采用一片TLC320AD50C,只需初始化其寄存器1、寄存器2和寄存器4。

TLC320AD50C与TMS320C30DSP芯片的连接

TMS320C30是TI公司浮点运算DSP芯片中比较典型的一种,它的主时钟达到40MHz,采用32位 浮点运算处理器,可以实现自适应信号处理和信号转换等高速浮点运算,是一种性价比很高的产品。

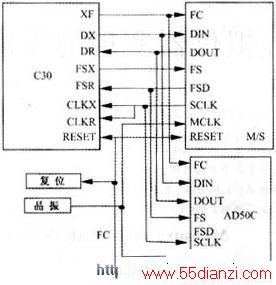

以下采用TLC320AD50C和TMS320C30的接口电路完成数据的采集和TLC320AD50C寄存器的读写 过程。TMS320C30和TLC320AD50C的接口电路如图4。

图4 TLC320AD50C和TMS320C30的接口电路

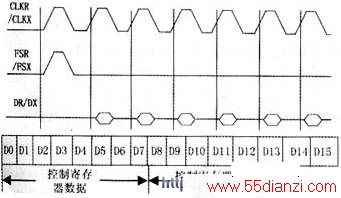

芯片连接的主要引脚有复位信号RESET;同步信号:AD50C上FS,FSD(延迟帧信号),TMS320C30上FSX(帧发送信号),FSR(帧接收信号);数据读写信号:DIN,DOUT,DX,DR;时钟信号:SCLK,MCLK,CLKX;二次通信请求:AD50C上FC, C30上XF。在时钟信号作用下,C30的帧信号(FSX,FSR)及数据的传输(DR,DX)时序图如图2。片外复位电路提供上电复位,晶振电路可提供 10MHz以上的主时钟频率,数据采样频率和其他时钟信号均由此频率分配。C30与AD50C之间有两种通信格式,即主串行通信格式和二次串行通信格式。前者用来接收和发送转换信号,后者在有请求的时候才进行二次通信。在主串行通信格式时,有两种数据传送模式:16位和15+1位,可通过控制寄存器设定,省却情况下为15+1位。采用15+1位传送模式,其最低位D0为非数据位,输入DAC数据的D0位为二次通信请求位,输出ADC数据的D0位为M/S脚的状态位。

二次通信只有在发出请求时产生,当首次通信采用15+1位模式时,可以用D0进行二次通信请求,当首次通信采用16位模式时,则必须由FC脚输入信号来产生二次通信请求。二次通信数据格式如图5中所示,其中D7~D0为控制寄存器数据,D12~D8为控制寄存器地址,D13=1为读控制寄存器数据,D13=0对控制寄存器写数据。通过二次通信,可实现TLC320AD50C初始化和修改TLC320AD50C内部控制寄存器。

图5 二次通信数据格式及时序图

数据采集电路及通讯软件实现

主AD50C的FSD接到从片的FS端,见图6。

图6 TLC320AD50C主从通信连接图

首先对相关寄存器进行设置。如果需要8kHz采样速率的模拟信号,且送到TMS320C30器件的时钟输入频率是30MHz,则下面的值应该加载进C30串口和定时器。

具体通信过程如下:AD50C数据输入输出与C30数据接收管脚相连,AD50C发出的帧频信号通过FS脚与C30达到同步,FSD为同步延时信号,主要用来扩展主从器件,AD50C上M/S可控制AD50C的主从方式。C30中时钟和同步信号脚可用软件设置成外部输入,这样数据发送/接收,帧同步,时钟信号均由AD50C产生,主时钟(MCLK)信号由晶振提供,FC、XF端作为二次通讯请求,假设数据传输格式为16位,则FC高电平时发出二次通讯请求。

具体通信过程如下:AD50C数据输入输出与C30数据接收管脚相连,AD50C发出的帧频信号通过FS脚与C30达到同步,FSD为同步延时信号,主要用来扩展主从器件,AD50C上M/S可控制AD50C的主从方式。C30中时钟和同步信号脚可用软件设置成外部输入,这样数据发送/接收,帧同步,时钟信号均由AD50C产生,主时钟(MCLK)信号由晶振提供,FC、XF端作为二次通讯请求,假设数据传输格式为16位,则FC高电平时发出二次通讯请求。

图8 程序的流程图

结束语:本文就两种典型的芯片连接进行了介绍,从而很好地实现了数据的采集过程中寄存器的数据读写,在实际中也得到了很好的应用。

本文关键字:接口 元器件特点及应用,元器件介绍 - 元器件特点及应用

上一篇:MAX7534简介及应用