介绍

随着消费者对智能电话需求的日益增长以及无线平板电脑的广泛普及,当今的移动因特网需要连接越来越多的用户,从而要求移动网络实现显著的容量增长。长期演进 (4G LTE) 能够以更低的成本提供更高的频谱效率与更大的容量。不断演进的 LTE-Advanced (LTE-A) 能够可实现具有更高带宽、更强吞吐能力与更高级天线技术的异构网络。同时,WCDMA 标准也在不断演进发展,具有更高的带宽以及更强大的吞吐能力。毋庸置疑,市场需要推出多标准基站。其结果是,部署在基站中的片上系统 (SoC) 器件不仅需要支持 LTE,还需要同时支持WCDMA 及其它原有标准。作为当今无线基站部署所采用无线基站 SoC 的领先供应商,德州仪器 (TI) 在该市场领域拥有长期成功的历史。在本白皮书中,我们将与大家分享我们 10 余年积累的“学习周期”体验和我们最新开发的无线基站 SoC —— TMS320CTCI6616和TMS320CTCI6618。

自无线网络诞生以来,其数据吞吐能力已实现快速增长。对营运商来说,最终的衡量标准是频谱每赫兹承载的比特数,以及实现特定吞吐能力所需的相关成本及功耗。一直以来,在无线标准升级的每一个转折点,TI 都无一不为基站设备带来价值与创新。如今,TI 的基站 SoC 只需少量电路系统即可处理无线基带第 1 层 (L1)、第 2 层 (L2) 与传输功能。TI 10 余年的丰富经验建立在成功的部署周期之上,主要体现在在以下方面积累的丰富知识:

1. TI 在最新的半导体工艺技术节点上成功推出众多器件,不仅能够实现显著的性能提升,同时还能大幅降低成本及功耗;

2. TI 在 DSP 技术领域拥有稳固的领先地位。毋庸置疑,无线基站需要为全球无线标准的传输与接收提供充分的数字信号处理能力。TI 拥有强大的实力,能够利用其行业领先的半导体工艺技术持续推出数字处理性能不断飞速发展的未来产品。各种优势全面结合,即能为市场推出高性价比的解决方案;

3. TI 始终致力于改进其高性能多内核 SoC。虽然无线基站的大多数功能都能够由 DSP 执行,但 DSP 最为擅长的则是与目标加速器相结合来实现各种优化目标,其中包括实现极高的单位频率吞吐能力、单位功率吞吐能力以及低系统成本等。在将硬件加速与业界领先 DSP 相结合以减轻无线标准的处理方面,TI 极为成功,能够以极低的成本与低功耗实现前所未有的吞吐能力。

TI 基站创新的第三个主要部分是本文的重点所在,即 TI 为基站 SoC 创建可配置硬件加速器的成功战略。在决定将无线信号处理链上的哪些部分转移到可配置硬件加速模块中时,有若干关键问题需要考虑,其中包括:

2

1. 无线信号链的哪些部分发生重大变化的可能性最小,而且哪些应基于成熟的标准之上?

2. 在候选功能中,设备制造商能否添加其自己的知识产权 (IP),以提供高级功能与差异化?

3. 无线信号链上的哪个部分具有最高的处理强度(如果在 DSP 的软件中实施时,需要最高的 DSP MIPS)?

4. 分配在硬件中的哪些功能可以简化并加快开发与测试?

5. 为确保全面的多内核能力与峰值加速器性能,需要何种类型的 SoC 基础局端?

要解决上述的第一个问题,需要确保无线处理标准的这些部分(无论仍处于开发中还是处于实验阶段)都将由 DSP 负责处理,这样营运商或 OEM 厂商才能实现解决方案的差异化。在对各种信号链功能及使用模型的 MIPS 要求进行分析后,就可以确定哪些功能应被移入硬件加速器,从而在降低成本和加快投产进度方面获得显著优势。

除了各种基于硬件的加速器外,TI 还创建了一种可确保实现高效率零复制数据流的创新型 KeyStone 架构,从而能够在内核、加速器以及外设之间实现非阻塞的系统互连。此外,该架构还能确保协处理器得到充分利用。它还可以减少中断及软件上下文环境的切换次数,以最大限度地实现所有内核的最佳利用,从而使所有系统组件都能得到全面利用。

确定系统优化的机会

确定新基站 SoC 设计方法的第一步,是考虑新一代基站的预期性能要求并理解其对SoC 设计的影响。

TCI6618 具备一系列针对新一代基站的用例目标参数。由于 TI TCI6488 是目前应用于基站的领先 SoC,因而其是一种非常适用于基线分析的器件。

下列各参数基于 LTE 系统中 TCI6488 器件的性能:

天线:2x2 发送与接收

带宽:20MHz

数据率:150 Mbps 下行,75 Mbps 上行

LTE 物理层概览

LTE 物理层需要对每个物理层通道进行高强度的信号处理。主要的物理层通道如下:

下行通道:

PDSCH:物理下行共享通道

PDCCH:物理下行控制通道

采用 TI 多标准基站 SoC 实现性能、效率与差异化的全面提升 2011 年 2 月

上行通道: 3

PUSCH:物理上行共享通道

PUCCH:物理上行控制通道

PRACH:物理随机访问通道

对于每个数据和控制通道而言,可将物理层处理分为两个主要的功能模块:比特率与 IQ 采样处理。

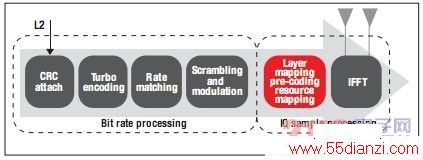

图 1 显示的 PDSCH 信号链由如下方面构成:

IQ 采样处理 — 处理 LTE 物理资源,将其映射到天线的不同层并转换为 OFDM 符号以用于空中传输。

比特率处理 — 处理来自 L2 的传输模块,通过计算循环冗余校验 (CRC) 并将其附加给传输模块来启动处理进程。如果传输模块大于 6,144 位的最大允许代码模块尺寸,则执行代码模块分段。在进行通道编码前,要进行新的 CRC 计算并将其附着于每个代码模块上。

图1 介绍了 LTE 下行链路中的主要功能模块。

图 1 - FDSCH 信号处理链

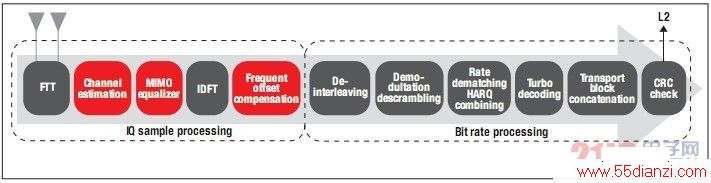

PUSCH 是 PDSCH 的反向过程,同样含有下列 IQ 样本与比特率处理:

IQ 样本处理 —— 处理接收到的 OFDM 符号物理资源。这涉及通道估算与最大比率合并 (MRC) /多输入、多输出 (MIMO) 均衡,以从各个天线分离用户数据。

比特率处理 —— 为在 L2 内实现进一步处理而进行的通道解调、解多路复用、错误校正与解码。

图 2 所示为 PUSCH 的信号处理链:

图2 - PUSCH 信号处理链

分析 TMS320TCI6488 中的 LTE 物理层处理 4

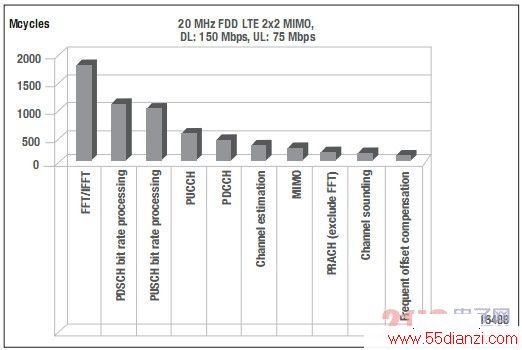

TCI6487/8 是 TI 最新系列的多内核 SoC,由三个 C64x+TM CPU 内核构成。采用这种 SoC 的运营商已有数百家,年出货量数百万片。通过分析 TCI6488 的 LTE 性能,可以深入了解如何构建新一代的高性能 SoC。图 3 所示为在 TCI6488 上采用 2x2 MIMO、150Mbps 下行吞吐速率及 75Mbps 上行吞吐速率时,20 MHz LTE 的周期占用数及分布。

图 3 - TCI6488 上的 LTE 物理层处理

从图上可以明显看出,FFT/IFFT、PDSCH 比特率处理、PUSCH 比特率处理与 PUCCH 占用了总 DSP 周期中的大部分。

为进一步改进总体系统性能,满足新一代 LTE 系统的要求,必须设计出具备良好均衡性且可扩展的架构,以便最大限度地发挥 SoC 的多内核计算性能。这就要求最大限度地提高系统的互连吞吐量,并将存储器存取与数据传输时延降到最小。

通过对 LTE 要求的总处理周期进行分析,我们发现通过增强 DSP 内核的信号处理能力,不仅能够减少处理周期的总数量,而且还能增大系统容量、提升性能。最新推出的 C66x DSP 内核通过将 C64x+ 的乘/累加 (MAC) 能力锐升四倍可实现这一目标。此外,新内核还同时集成了定点与浮点功能,并可为矢量处理与矩阵处理提供新的指令。

如快速傅里叶变换 (FFT) 与快速傅里叶逆变换 (IFFT) 等特定函数需要在 LTE 信号链上的许多地方执行,并且用于在时域与频域之间进行数据转换。FFT 与离散傅立叶变换 (DFT) 已属成熟算法,因此它们有可能作为硬件加速的候选以用于释放 CPU 周期,这样 DSP 内核就可用于执行客户差异化功能。

本文关键字:暂无联系方式通信基站-中继,通信技术 - 通信基站-中继