1 ����

��WCDMA�У����ž�����һ��α��������ж���Ƶ�������ˣ����źŽ��м��ܡ�������·�����ŵ����ŵ������������û���������·���ſ�������С�����ŵ���WCDMA����Gold����Ϊ��Ƶ���е����롣Gold������M������Ӷ��ɣ������ײ�������������������ŵ㡣���Ľ���������������ɹ��̺������FPGA��ʵ�֡�����VerlogӲ���������Խ��й�����������д�źŵ������£��踶�����ֵ����ʱ���źŵ������£��������������I��Q���С�

2 ��������Ľṹ

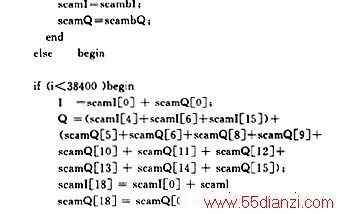

������·��18���صij�ʼֵ���ɲ���218-1 = 262 143�����룬���Ժ���0…262 142�������������е����붼���á������Ϊ512�飬ÿ�����1�����������15���������롣

�������������Ϊ��n=16*i�������,����i=0…511����i�鸨�����������Ϊ16*i+k������ɣ�����k=1…15��

ÿ�����������ͬһ���ڵ�15������������һһ��Ӧ��ϵ����i�����������Ӧ�ڵ�i�����롣

�����������ַ�Ϊ64�������飬ÿ������8�������롣��j���������ɻ�������16*8*j+16*k��ɣ�����j=0.63��k=0.7��

ÿ��С�����ҽ���һ���������롣����CCPCH�ͻ���CPICH�����û������봫�͡���������������ŵ������û������������ڴ�С���Ļ�������ĸ������뷢�͡�

��������ͨ��������ʵ��������ϳ�һ�������������ɡ�������ʵ�����ж����������ɶ���ʽΪ18�� ���ضϳ���Ϊ38 400��m����ģ2�����ɡ�����������о��ɽضϵ�Gold������ɡ�������10ms������֡Ϊ�����ظ�����x��y�ֱ��ʾ���������У�x�����ñ�ԭ����ʽ1+X7+X18����GF(2)���ϣ����ɣ�y�����ɱ�ԭ����ʽ1+X5+X7+ X10+X18���ɡ�

��zn��ʾ��ѡ���������n���������У���x(i)��y(i)��zn(i)�ֱ��ʾ����x��y����zn�ĵ�i�����ţ�m����x��y���ɷ������£�

��ʼ״̬��

���з��ŵĵݹ鶨��Ϊ��

![]()

��Щ����������������Ĺ���ת����Ϊʵ������Zn��

![]()

���n������Sdl,n��������

![]()

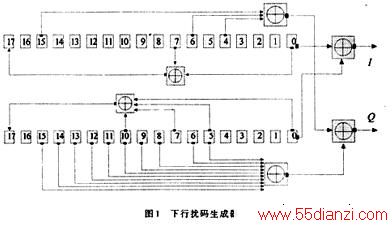

��ע��������λ0~38 399�������ظ���ͼ1��������·���뷢�����Ľṹʾ��ͼ��

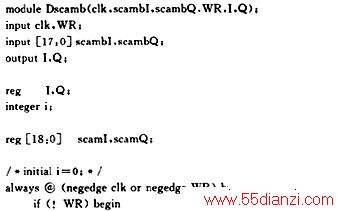

3 ���ɴ���

4 ������

��Verilog HDL����������������ԭ��������ƣ�����ͬ������Ʒ���������������������ʽ���������еij����롢�Ͷ����롣

���Ĺؼ��֣�WCDMA ͨ�Ż�վ-�м���ͨ�ż��� - ͨ�Ż�վ-�м�