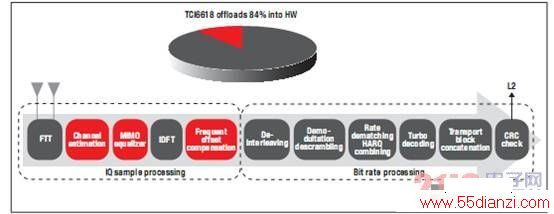

图 11 - TCI6618 中的 PUSCH 处理

这些图清晰地表明,BCP 可显著提高 LTE 的性能。由于所有比特率处理均被自动路由到 BCP,因而可大大简化软件设计并降低时延。在这样的数据速率(150 Mbps 的下行/ 75 Mbps 的上行)下运行,处理时延还不足 70 微秒。

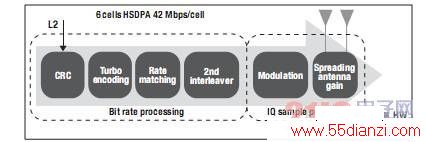

BCP 不仅可以为 LTE 实现上述优势,而且也能为 WCDMA 分担比特率处理任务。与针对码片级扩频/解扩的 RAC 与 TAC 结合使用,可实现 HSDPA 信道几乎完全在硬件中处理。图 12 显示了 TCI6618 中的 HS-PDSCH 信号处理链。

图 12 - TCI6618 中的 HSDPA HS-PDSCH 处理

16

TCI6618 能够支持如下方案:具备 6 个使用 2x2 MIMO 的 HSDPA 单元,且每个单元的下行吞吐量为 42 Mbps。在该例中,有超过相当于 9 GHz 的 DSP处理任务被分配到专为 HS-PDSCH 信道设计的硬件中处理。

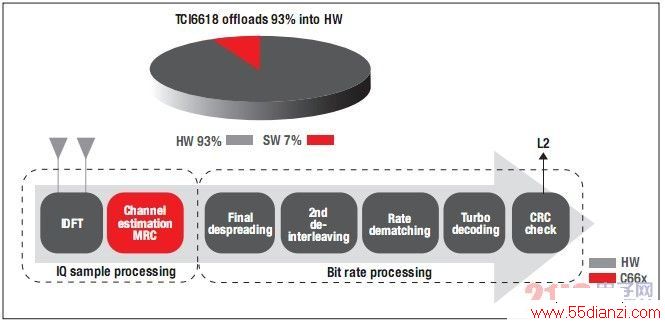

同样,对于 WCDMA 上行信道处理,图 13 显示了 HSUPA E-DPDCH 处理的信号链与周期分布。

图 13 - TCI6618 中的 HSUPA E-DPDCH 处理

结论 业界最佳的 TMS320TCI6618 与 TMS320TCI6616 SoC 经过精心设计,可支持无线数据的发展变革,以及从以语音为中心到以数据为中心的处理的演变过度。新的比特率协处理器 (BCP) 及 KeyStone 架构可为无线基站提供可实现最高性能的 SoC。集成定点与浮点功能的 C66x 内核能够为市场上功能最强大的 DSP 提供系统所需的灵活性。TI 借助多年来在无线基站基础局端领域积累的广博的专业知识和丰富的系统和现场经验成就了卓越的设计方法,能够实现业界最可靠、最高级的解决方案。在基于协处理器实现的加速功能和在 DSP 内核中实现的灵活处理功能之间,TMS320C6618/6 架构实现了完美的平衡,不仅能够为多样化的基站市场实现所需的差异化功能,而且还能继续帮助备选解决方案实现巨大的性能改进。

本文关键字:暂无联系方式通信基站-中继,通信技术 - 通信基站-中继