1 引言

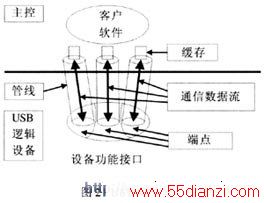

通用串行总线 ( USB ) 是 Intel 公司 1996 年提出、由康柏等七家公司联合制定的一种新型接口技术。 USB 历经七年的发展,目前已经到了 2 . 0 版本。由于数据传输速率高,传输可靠,连接灵活,成本低廉,所以 USB 在 PC 领域获得了广泛的应用。USB 系统中包含的硬件和软件如图 1 所示。所有的 USB 传输事务都在 USB 系统软件控制下进行,

系统软件包括 USB 设备驱动、 USB 驱动和 USB 主控制器驱动程序。 USB 设备驱动程序负责与 USB 设备进行通信,它提供了 USB 设备驱动程序和 USB 主控制器之间的接口。这些软件负责把客户请求转换为一个或多个传输事务进行处理,然后被直接送往 USB 目标设备或者被目标设备发出。

&nbs p; 每个 USB 传输事务包含一个或若千个信息包,包括令牌包、数据包、握手包、专用包,信息包采用了非归零编码 (NRZI) 的串行传输方式。为了便于接收端信号的时钟恢复,传输中的串行数据还要进行位填充处理,使串行信号不跳变的最长时间为 6bit 。

2 USB 通信模型

USB 系统采用的塔形拓扑结构使 USB 系统只能采用共享总线的方式进行通信,即所有设备只能通过一条数据通路与主控制器进行通信。在总线中,每个设备具有 - ―个地址,而且每个设备中的若干端点也被分配了端点地址。所有通信的数据来源或目的都是基于这些端点地址,所以从客户软件看来,对端点的操作就像处于一个独立的管线中,如图 2 所示。

在 USB 系统中,对端点的操作被设备驱动程序分解为 IRP(I/Orequest PACkets) 。 USBHOST 把这些 IRP 分解为基本的传输事务 ( 如 IN , OUT 等 ) ,安排在相同或不同的帧中。每个传输事务包含若干信息包,其中包含了与 HOST 通信的设备地址和端点地址,只有地址对应的设备或端点才能响应 HOST 发出的信息包。

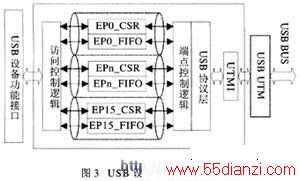

基于以上分析,可以构造出设备端 SIE 通信模型,如图 3 所示。在这个模型中,由端点控制/状态寄存器 (CSR) 和端点 FIFO 组成的管线记录了端点的状态和通信的有效数据。端点控制逻辑用于端点选择及端点访问控制。通过 USB 设备功能接口,设备功能软件可以方便地以管线形式对端点进行状态控制,以实现 USB 通信。

3 USB SIE 电路结构和设计

3.1USB SIE 电路结构

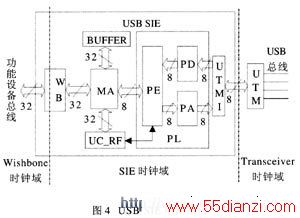

根据 USB 通信模型 ,构造的 SIE(serial inter face engine) 电路结构如图 4 所示。主要包含 UTMI , PL( 由 PD , PA , PE 组成 ) , MA , UC_RF , BUFFER , WB 等功能模块 , 可以完成 USB 速度识别、解析信息包、组构信息包、底层协议处理、缓存管理、中断请求等功能。此外它还需要外接控制器才能完成 USB 通信。

3.2 USB SIE 各功能模块说明

UTM(USB transceiver macrocell) 主要完成两个功能:从 USB 总线上接收数据,经过 NRZI 解码和位剥离后,转换为 8 位并行数据,传送给 SIE 中的 UTMI £》或从 UTMI 接收 8 位并行数据,经过 NRZI 编码和位填充后,发送到 USB 总线。

UTMI(UTM interface) 的主要功能有两个:接受 PD , PA 的控制,在 UTM 数据线上输入或输出数据:检测总线状态以及识别总线速度。

www.55dianzi.com

PD(PACket dISAssembler) 将接收到的信息包数据进行解析,解析出包标识 (PID) 、端点地址和 Function 地址以及包含在包中的有效数据。在解码时,要对必要的令牌包进行 CRC5 校验,对数据包进行 CRCl6 校验。

PA(packet assembler) 根据 PE 送来的 PID 组织相应的信息包,把要发送的数据安排在相应的数据包,或者组织令牌包。发送令牌包时,不必产生 CRC5 校验位。在发送数据包寸,需要把有效数据的 CRCl6 校验位放在包末尾一起发送。

PE(protocol engine) 可以对 IN,OUT 以及 SETUP 事务进行单线程处理 ( 串行总线不能同时进行两个以上 USB 传输事务 ) ,且确定当前传输事务要操作的端点地址,所有对 MA 和 RF 的当前操作 都基于这个端点地址。 PE 要根据当前端点的配置或当前状态处理传输事务,并在传输事务中实时更新控制/状态寄存器 CSR 。 SIE 还能通过 CSR 中的中断向量请求设备总线的控制支持。 PD , PA , PE 三个模块组成了 USB SIE 的协议层 (PL) 。

MA(memory buffer arbiter) 管理数据的流向, WB 通过最高位地址选择读写目标是 FIFO 还是UC_RF ; PE 则通过端点地址选择相应的 FIFO 和 UC_RF 。在对 FIFO 的操作上, PE 比 MA 有更高的优先权。

UC_RF(USBcorer egister file) 最多支持 16 个端点。每个端点的 CSR 分别存储本端点的当前状态。每个端点的 CSR ,包含 5 组寄存器,分别为配置 CSR 、协议 CSR 、进程 CSR 、中断状态 CSR 和中断屏蔽 CSR 。它们可以接受 MA 和 PE 读写。

BUFFER(USB SIE buffer) 对相应的端点收发数据进行缓存,最多支持 16 个端点。每个端点 FIFO 占用固定的 SRAM 区域,分别有读指针和写指针指向该端点对应的区域。

WB(Wishbone interface) , 标准 Wishbone 接口,连接两个不同的时钟域,在数据传输时要把两个时钟域分割开。

4 USB SIE 验证

4.1 验证环境

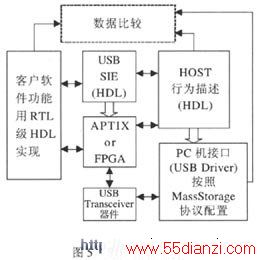

所设计的 USB SIE 集成了符合 USBl.1 规范的 UTM ,可以外接 USB2.0 规范的 UTM 。所设计的 SIE 实现了图 4 所示的 SIE 电路,完成了图 3 所示通信模型的所有功能。通过修改配置文件,可以定制电路的一些参数和结构,如包含的端点数目以及每个端点的通信模式等。 USB2.0SIE 的验证环境如图 5 所示,它是围绕 USB SIE 这个 IP 核展开的。

为了验证电路的功能,需要建立一个 USB HOST 端的 HDL 行为模型,这个模型模拟了一个真实 HOST 的行为过程,如上电检测、速度识别、标准设备请求等过程,并且可以检测 USB 设备应答数据是否正确。另外还可以启动对 USB 设备容错性能的检测,通过在 USB 通信中插入随机错误信息,检测 SIE 通信的健壮性以及 SIE' 陕复机制的可靠性。最后这个模型还要能够保证 SIE 的 HDL 代码有足够的覆盖率,即完成对 SIE 所有工作情况的测试。这个模型可以测试多种 USB 设备,以后还可以作 USB 设备的后续开发。

我们还设计了一个专用的控制器,它可以实现 SIE 的上电初始化过程 ( 向 SIE 中控制/状态寄存器堆写入初始数据 ) 、 SIE 中断处理并完成 USB 传输事务、使 SIE 摆脱异常状态等功能。这个专用控制器和 USB SIE 一起构成一个完整的 USB 设备。

www.55dianzi.com

在硬件验证时, FPGA 采用 ALTERA 公司 Stratix 系列的 EP1S80B956C6 。由于时钟速度和器件选购的限制, Transceiver 器件采用了 USB l.1 的收发端器件 PDIUSBP11A 。这样实际通信只是 USBl.1 全速以及低速的通信,虽然 USB2.0 的某些特性验证不到,但是在已有的条件下,已经验证了 USB2.0 在全速模式下工作的所有特性。 USB 设备的硬件验证装置如图 6 所示。

本文关键字:暂无联系方式综合-其它,单片机-工控设备 - 综合-其它