设计规范

为了满足当今大多数较小规模的LCD显示应用的实际需要,本文所设计的LCD驱动电路IP核芯片具有64个COM(行)和64个SEG(列)输出,有高速的8位并行MCU接口及串行接口,芯片内含有存储显示数据的RAM,并专门设计了10个控制端,可以方便灵活地进行控制。它主要有以下几个主要功能:

1、为液晶显示屏提供扫描时序信号和显示信号数据;

2、支持以总线形式直接与MCU相连;

3、可驱动不同规模的LCD(n×m),n可以连续取值(n=0~63),m只可取8的倍数(m=8k,k取自然数);

4、支持IP核之间的级联以驱动较大规模的LCD,最大分别支持4个IP核行间级联和列间级联;

5、可以提供较宽的驱动输出电压范围以适应不同的LCD器件;

6、提供画中画、分屏显示等功能。

IP核的设计

本文按照“自顶向下”的设计方法,首先对芯片进行层次化功能划分,同时参照已有的LCD驱动芯片的设计经验, 并结合“自底向上”的设计方法对部分模块进行设计, 最后根据系统设计框架对各模块进行协调, 并进行芯片的整体功能验证, 从而达到了设计规范的要求。

系统结构

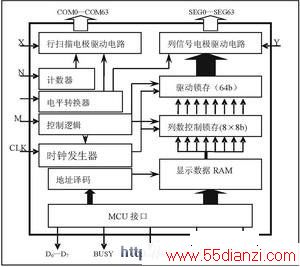

本文设计的IP核系统结构如图1所示。该IP核主要由下列几个模块组成:行扫描和列信号驱动模块、电平转换器、可预置数环形计数器、数据锁存模块、控制逻辑模块、显示数据RAM与地址译码模块、MCU接口模块。其中有的大模块还可细分为若干子模块。

图1 IP核系统结构

www.55dianzi.com

各模块设计

MCU接口模块

MCU接口模块是 IP 核与外部控制器(MCU)通信的接口,是数据传输的通道。MCU通过该接口对 LCD 驱动 芯片写入命令、读出状态或显示数据。同时该接口也接受命令译码器的控制,从而使读写与内部操作相结合。该芯片由较为复杂的内部组合逻辑和时序逻辑电路实现,可以兼容目前两种主流的MCU控制信号,支持串/并行两种数据操作方式。

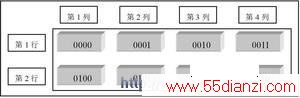

该模块内部除了包含现有常用LCD驱动电路的MCU接口模块中常用的几个子模块,如数据总线(8位)子模块、忙状态检测子模块、读写控制子模块、MCU释放子模块外,新加入了一个行级联和列级联控制子模块。数据总线主要用于内外部数据交换;忙状态检测子模块用于判断MCU状态,产生系统忙标志信号来协调信号的读写操作和接收内/外部复位信号;读写控制子模块用于产生正确的读写控制时序;MCU释放子模块的功能则为通过逻辑组合,在芯片执行“读-修改-写”过程时,释放MCU,以便MCU可以同时执行其它操作;而新加入的级联控制子模块的主要功能是实现IP核之间的行级联和列级联,最多可支持16个IP级联(行列各4级),CS0~CS1是行级联控制端,CS2~CS3是列级联控制端。举例说明,假设有一种LCD(128×256),可用8个IP核来驱动,设置时分别令CS为0000、0001、0010、0011、0100、0101、0110、0111,就可以构成2×4的驱动IP核阵列,其排列示意图如图2所示。

图2 IP核级联排列图(24)

显示数据RAM与地址译码模块

该模块主要用于存放将要显示的数据,在MCU接口和信号驱动电路之间起缓冲器的作用,以保证显示数据的稳定输出。该模块包括存储显示数据的RAM阵列和地址译码器两个子模块。首先,由列地址电路提供列地址,通过列地址译码器选中一列8位的RAM存储单元,MCU通过接口对其进行读/写;然后,由行地址译码器对RAM以行为单位进行扫描,结合显示数据锁存电路可以实现整行数据的输出,通过电极驱动电路输出到液晶显示器以供显示。

数据锁存模块

该模块包含两个子模块:列数控制锁存子模块和驱动锁存子模块。列数控制锁存子模块由k个并联的8位数据锁存器构成,主要作用是锁存数据总线上的数据,在控制逻辑模块的控制信号和时钟信号作用下把从RAM上输出到8位数据总线上的显示数据信号分别锁存在相应的8位数据锁存器中,64位数据需要8次,每次8位输入。驱动锁存器子模块是一个由64个1位锁存器并联而成的64位驱动锁存器,它的作用是在控制逻辑模块的控制信号和时钟信号作用下把上面8个8位数据锁存器里传输来的m位数据一次全部锁存起来,然后输入到后面的列信号电极驱动模块。

控制逻辑模块

该模块的主要作用是控制信号数据传输和选择列信号线的数目。可以通过列数控制输入端M来控制列数控制锁存器子模块、驱动锁存器子模块和时钟发生器来实现适用于不同规模LCD的功能。根据需要,通过向列数控制输入端M输入不同的数值,来控制有多少位列数控制锁存器处于工作状态,其他的锁存器单元则置为空闲态。在工作周期内把显示数据RAM中的数据通过8位数据总线锁存到对应的列数控制锁存器中,然后在一个时钟信号控制下一次锁存到驱动锁存器中,以作为电极驱动模块的输入信号。这样,IP核可以实现控制选择驱动列数的功能。当M为“000”时,列数控制锁存器的低8位(第一个锁存器)工作,其它的全置闲,对应的列电极是SEG0~SEG7;当M为“001”时,列数控制锁存器的低16位(第一和第二个锁存器)工作,其它的全置闲,对应的列电极是SEG0~SEG15;依次类推,直到列数控制锁存器64位寄存器全部工作,对应的列电极是SEG0~SEG63。

www.55dianzi.com

电极 驱动 模块

该模块主要含有四个子模块:行扫描电极驱动子模块、列信号电极驱动子模块、电平转换器和可预置数环形计数器。电平转换器的作用是根据实际应用的需要,通过外加的控制信号将逻辑信号的电压转换为实际的 LCD 驱动电压,并输出到驱动模块;行扫描电极驱动子模块的作用是给行电极提供一定周期的扫描信号脉冲;列信号电极驱动子模块的作用是把来自锁存器的数据施加到相应的列电极,与行电极的扫描信号来建立交流驱动电场,从而驱动LCD器件的显示。

本文关键字:通用 综合-其它,单片机-工控设备 - 综合-其它

上一篇:ASIC设计中验证工具选择实例