��������

������ CPLD �����ӿɱ��������������������桢��֤������ISP����ϵͳ�ɱ�̣���Ӳ�����Զ��dz����㣬���Կ������ں̣ܶ���I/O�������趨������CPLD���ר��оƬ�Ǵ���������VB��һ���������ĸ����ԣ�Ӧ����� ͨ�� �ؼ���д��λ����ͨ�ų���ʮ�ַ��㣬���̼��������CPLD�� PC ͨ�ŵ��ص㣬����д����λ������λ���ij�������Ը��ٵĴ���ͨ�š�

����1 ��λ������λ��ͨ���ص���

�������ݴ���ͨ�ŵ�Э�飬���ʹ�������һ���ǣ�1����ʼλ��n������λ��1������ֹͣλ��������������ʼλ�Ժ�������俪ʼ����������յ�˫���趨��ͬ���Ĵ���λ����ֱ��n������λ�����Ժ���ֹͣλ����λ������λ���ĵ�ƽ����ͬ������ͨ��RS-232��ƽ��ת����������֮�����RS-232��ƽת��оƬ���ɡ���λ������λ���Ĵ������첽���䣬��������Ҫ��һ���ο�������������ٶȼ������ʡ�ͨ��˫��ȡ��һ����ͨ���ٶ�bps��ָ����ÿһ���������͵�λ��������������ҵ���ϣ�һ��9 600 bps��������ٶȣ������ڸ��˼����PC���ṩ�Ĵ����ٶȿ� 115 200bps������921 600 bps������ Ϊ���õĵ�Ƭ��MCU�������ǹ������ԣ�������Ϊ��λ�������ṩ��ô�ߵIJ����ʣ���ʹ�ǽϵ͵IJ�����Ҳ���ܲ����������ڴ������Ͻ����豸Ҳ���ṩʱ��ʹ����ߵĴ����ٶ�Ҳ���ԡ�CPLD�������Ƿǹ������ԣ�Ҳ����˵�����ζ�������ж�����ͬʱ���еĶ����Ǵ��еģ�������ȫ�����ṩ�����ĸ�����λ��UART��Universal Asynchronous Receiver Transmitter����

����2 ���VB����

������λ����������VB6��д������VISUAL BASIC�����м����ѺõĽ��棬���ܹ������Ա�ĺ���������ӻ��ص�õ��˺ܺõķ��ӣ����е�MSCOMM�ؼ��dz������д����������Ͳ�IJ������Σ�ֻҪ�˽��Լ���Ҫ�IJ�������˳���д��λ�����������ڼ��ÿؼ��ĸ��������

����CommPort����ָ�����пڣ�

����PortOpen���������Ƿ��

����InPut��������Ĵ�����

����Output��������Ĵ�����

����InBufferSize�������뻺������С��

����OutBufferSize�����������������

����InputLen����һ���ɴ��ж˿ڶ����ַ������Ȼ��ֽڸ�����

����Settings�����豸�����ʡ���������λ��У��λ��ֹͣλ��

����InputMode������������������ͣ�������ʽ���Ƕ�������ʽ����

������λ������Ҫ����λ�������������Ҫ�뿼�ǵ������Dz����ʡ���������������͡����ڴ���λ������λ��������ݵ�������������´�������֮���ƣ���

����Settings 115200��n,8,1��������115 200bps��У��λĬ�ϣ�8λ����λ��1��ֹͣλ��������λ����������������Զ���������ʽ��ȡҪͨ�����µ�ת����

����Dim data() As Byte

����Private Sub Timer1_Timer()

����data()=MSComm1.Input

����For i="LBound"(data)To UBound(data)

����Text2.Text=data(i)

����Next

����End Sub

�����ڴ��ڴ�����£����ö�ʱ����ʱ����λ����ȡ���ݣ���ʾ�ڴ����С�ͨ������VB��ʱ���ؼ���interval���������ƶ�ȡʱ�䡣�ɼ�����λ������VB��д����ʮ�ַ��㣬����һ�ֳ����ģ�黯���ԣ�ֻҪ�Ѳ����������ܿ����ʵ�ֱ�̡�

����3 ��λ��ͨ�ų����д

����MAXPLUSII�������ೣ�õĺ굥Ԫ������������������㡢������������ROM��RAM�ȣ�������Щ�굥Ԫ�����IJ������������û��������趨������������ᵽ��IP����ʽ������CPLD��������нṹ����Ƶ����ƣ���ͬ��ε�IP��intellectual Property���˽����֡�����IP�˿��ظ����ã������������������Ч�ʣ��������ظ��Ͷ���������Ƶ�����λ����IP�ˣ�����һ�������ʡ���ʼλ��ֹͣλ�����趨�ĺ굥Ԫ��

����MAXPLUSII��AHDL��ALTEra Hard ware Description Language����Altera��˾��������ȫ������MAXPLUSII�е�һ��ģ�黯�����ԣ��ر��ʺ����������ӵ�������������㡢״̬������ֵ������������AHDL��ֱ������IP�ˡ�

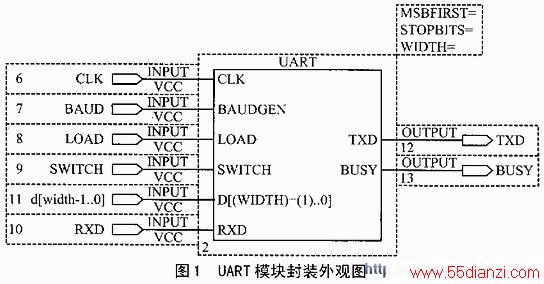

������Ƶ�����Ŀ����������ͼ1��ʾ��Symbol��������������û��趨����ͼ1�����Ͻǣ���ѡ�����ͣ��գ������������λ�����λ�����ݿ��ȡ�ֹͣλ�ȡ�

���������嵥���£�

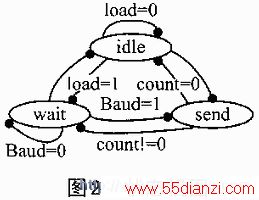

����CASE Ss IS --״̬��

����WHEN idle =>

����IF Load THEN

����Ss=wait;

����ELSE

����Ss=idle;

����END IF;

����WHEN wait =>

����IF Baud THEN

����Ss=send;

����ELSE

����Ss=wait;

����END IF;

����WHEN send =>

����IF count[]!=0 THEN

����Ss=wait;

����ELSE

����Ss=idle;

����END IF;

����WHEN OTHERS =>

����Ss=idle;

����END CASE;

����TxD=InShift[WIDTH+1]; --TXD����

����IF Ss!=idle THEN --����BUSY

����Busy=VCC;

����END IF;

����CASE Ss IS

����WHEN idle =>

����count[]=WIDTH+STOP_BITS; --�ȴ��͵�λ��

����WHEN send =>

����count[ ]=count[ ]-1;

����WHEN OTHERS =>

����Count[]=count[]��

����END CASE��

����CASE Ss IS --��������Ĵ���

����WHEN idle =>

����IF MSB_FIRST= =��YES��GENERATE

����DTMP[]=D[];

����ELSE GENERATE

����FOR each_bit IN 0 TO WIDTH-1 GENERATE

����DTMP[WINDTH-1-each_bit]=D[each_bit];

����END GENERATE;

����END GENERATE;

����InShift[]=(1,0,DTMP[]);

����WHEN send =>

����InSift[WIDTH+1..1]=InShift[WIDTH..0];

����InShift[0]=VCC;

����WHEN OTHERS=>

����InShift[]=InShift[];

����END CASE;

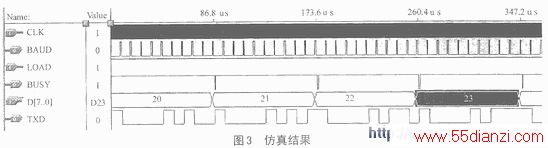

����ͼ3Ϊ���沨�Σ�ϵͳʱ��CLKΪ6MHz��50��Ƶ��õ�����Ϊ868ns��ʱ��BAUD����������Ϊ115 200 bps���趨Ϊ�Ӹ�λ����λ���δ��ͣ���ʼλ1λ���͵�ƽ��8λ����λ��1��ֹͣλ��Ϊ�ߵ�ƽ��ͼ3����ʾ�ֱ���ʮ������20��21��22��23������������00010100 00010101 00010110 00010111���������LOAD�ź�һֱ��Ч���ɼ�������1�������ܹ���10λ��1����ʼλ��8������λ��1��ֹͣλ�����ղ�����115 200 bps������1��������Ҫ��ʱ��Ϊ86.8��s��������ȳ�������� CPLD �����ƣ��ȵ�Ƭ��MCU���д���Ҫ����10�����ϡ������λ��UART����������ٶȻ��������ӽ�MCU���д����100������������Ϊ921 600 bps��

����������ͨ�������Ժ�ͨ����̵�Ž����ɵ�pof�ļ���ISP�����߱�̣���ʽ���ص�CPLD��EPM7128LC84-6�����RS-232��ƽת��оƬHIN232CP��������ƽת����CPLD�� PC ���ӿ� ͨ�� ����λ����VB��д��������֤�����ڸ�������£�ͨ��������

���Ĺؼ��֣�ͨ�� DSP/FPGA��������Ƭ��-�����豸 - DSP/FPGA����