介绍

在嵌入式微控制器应用中,通常都要用到非易失性存储器。无论是掉电时维持需要保存的设置,还是存储公司的重要记录,可靠的非易失性存储器都是现代微控制器领域的一个基本单元。

非易失性存储常常采用外部串行存储器实现。多年以来,该领域用到了数十亿颗类似存储器件,它们的可靠性得到了的广泛认可。目前,存储器可以做到几百字节到1兆字节甚至更大的容量,在每一个需要保持设置的设备中,都能找到这样一个紧凑、廉价的器件。

包括 EEPROM 、闪存和旋转式存储器在内,所有类型的非易失性存储器都面临一个共同的问题:写周期被中断时,数据会丢失。一旦在写周期执行过程中掉电,那么即使再恢复电源,也很难修复损坏的数据。 本文提出了一种基于事务的提交-回退机制,用于保护一个外部串行EEPROM存储器件的内容。这些措施同样适用于大多数M

AXQ微控制器的内置EEPROM。

I2C EEPROM的特点

串行存储器件有多种接口,但最常用的接口是I2C接口。这种总线接口有很多优点:高度标准化的接口;控制器和存储器之间只需两条线;而且具有灵活的时序要求,可以由软件驱动。一个I2C主机可以驱动很多I2C从机,从而最大程度减少了主机的引脚数。

在所有EEPROM器件中,写周期都要比读周期长的多。因为在写周期过程中,电荷需要借助隧道效应并通过绝缘层进行转移,而这个过程很费时间。虽然增加电压可以加快这个过程,但是过高的电压会导致绝缘层的介质击穿,从而损坏器件。典型的EEPROM器件写周期持续10毫秒左右;而读周期通常需要几百个纳秒。

为了显著缩短写周期的时间,许多I2C EEPROM器件采用页面模式。该模式允许将多个字节传送到缓存中,然后将数据一次性写入存储区。I2C存储器件的典型页面尺寸为32字节。因此,可以在一个写周期内向EEPROM填入32个字节。

这一点非常重要,因为串行EEPROM器件都具有特定的耐久度:即每个页面所能承受的写周期次数上限。典型的写周期次数从10,000到1,000,000次。然而,即使存储器件能够承受1百万次写周期,软件也会很快将其损耗殆尽。软件每秒仅执行100次写周期,那么不到3个小时就会耗尽器件的写周期次数。

考虑到这些基本的EEPROM特性,设计者为一个嵌入式处理器设计可靠的非易失存储系统时,需切记以下几点:

不要在同一页面上反复执行写操作。尤其是不要将某个页面设置成写入任何其它页面时都要更新的“目录”。

如果在写周期过程中电源被中断,必须提供以下机制:(1) 检测被中断的写操作;(2) 完成被中断的操作;(3) 或者将事件回退至写操作之前的状态。必须通过某些数据校验机制(校验和、CRC或消息摘要)来保证数据的完整性。

设计目标

虽然上面提到的EEPROM问题可通过多种非易失文件系统加以解决,但这样的文件机制对于小型嵌入式微控制器来说负担过重。很多文件系统需要更多的RAM,远远超出了小型微控制器所能提供的容量,而且对于多数应用,也不需要一个完整的文件系统。考虑到这一点,下面列出了EEPROM数据保护机制的设计目标:

精简:保护机制用于存储校验数据的空间不应超过EEPROM的10%,它应该只需要少量的计算开销。

块大小:被保护的块大小,应该和EEPROM的写操作页面大小一样。由于EEPROM器件的页面大小通常是2的偶数次幂,因此与每个块保留1或2个字节的做法相比,相同的尺寸大小更便于软件编码。

耐久性:每个保护周期不要对同一页面进行写操作。

可靠性:每次掉电情况下,数据都应是可恢复的。

www.55dianzi.com

这里提到的保护机制有6个接口函数:读、写、提交、回退、检查和清理。

读函数接收一个块编号和一个指向32字节缓存的指针。如果缓存地址和块编号处于有效范围内,程序就会将指定的块数据读入缓存,并校验数据的有效性。它会返回如下状态:有效读(valid read)、无效读(invalid read)、无效缓存地址(invalid buffer address)、无效页面编号(invalid page number)或保护失败(protection failure)。

写函数接收一个块编号和一个指向填好数据的32字节缓存的指针。如果缓存地址和块编号处于有效范围内,程序就会将

数据写入非易失性缓存,并标记缓存状态以准备提交。

提交和回退函数,是可以在写操作之后执行的互补型操作。提交函数将最近被写入的缓存数据复制到对应的存储区最终位置,并为下一个待写入的数据块准备好缓存结构。回退函数实际上就是一个“取消”操作。它消除最近一次写操作产生的效果,并为下一个写操作准备好缓存子系统。 检查函数读取存储器件的每个数据块,并检查存储数据的有效性。该函数还检查缓存子系统,以确保没有未执行的写操作。任何无效块或未执行的写操作都会使检查函数返回一个错误状态。

清理函数修复一个数据损坏的 EEPROM 。实际上,它将试图找出发生的错误,并采取相应的解决措施。关于这些函数的更多细节,参见下面的操作详解。

EEPROM结构

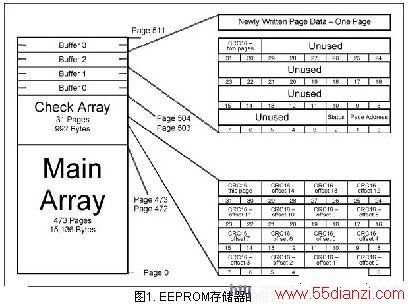

参考上面图1给出的EEPROM结构。EEPROM包含三个主要区域:

主存储区:EEPROM的最大区域用于存储用户数据。在一个16kB器件内,包括512页、每页32字节的存储空间。在这样的器件中,开始的473个页面专门用来存储数据。

校验存储区:EEPROM的第二个部分,用于校验主存储区每个页面的数据。校验存储区的每1页都包含15个16位的CRC值。每1页的最后1个CRC用于校验本页数据。校验存储区占用31页(从473到503页)。

缓存:EEPROM的最后部分,包含由8个页面构成的4个写缓存。每个缓存包含4个域:数据域,它包含32字节数据,执行下一个提交命令时,数据将被写入主存储区;地址域,它表示缓存数据要写入的页面地址;状态域,它表示缓存的状态(包括可用(available)、占用(oCCupied)和终止(expired)状态);16位CRC域,用来校验整个写缓存。缓存结构见图1所示。

这种EEPROM结构可以实现主要的设计目标。首先,由于主存储区每1页数据的校验结果都存储在另一个位置,所以页面的所有位都用于存储用户数据。其次,由于主存储区的每1页都通过校验存储区的特定字来校验,因此校验存储区不会有单点错误,并且也不会在每个写周期中都去更新整个校验存储区的同一页面。最后,使用4个写缓存分散了写周期带来的损耗。

操作详解

对于一个不带保护功能的EEPROM,具体操作非常简单。一个读周期简单地将字节从所选择的地址传送给主机;一个写周期将字节从主机写入EEPROM,并等待操作完成(大多数器件需要几个毫秒的时间)。然而,在一个提供保护的EEPROM环境下,读和写操作就比较复杂了。在以下各节中,对每个操作进行了分解,以便了解函数被调用时到底是如何操作的。

读操作

www.55dianzi.com

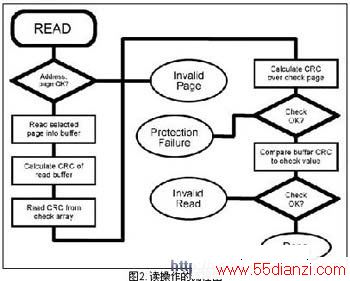

读操作这个最简单的接口函数,也是相当复杂的。图2给出了操作流程:

检查页面地址和缓存地址,以检验它们的有效性。如果地址无效,则就此结束操作,函数返回一个无效缓存地址或无效页面编号错误代码。将所选页面读入缓存,计算校验页面的地址,并将相应的校验页面读入暂存区,计算校验页面的CRC。如果校验页面的数据无效,则返回一个保护失败错误代码。

计算数据缓存的CRC,并将其与暂存区中对应读取页面的CRC进行比较。如果CRC匹配,则程序返回有效读代码;如果CRC不匹配,则程序返回无效读代码。无论结果怎样,实际读取的数据都保存在返回缓存中,以供调用读操作的程序使用。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术