电子电路中,共阻抗干扰对电路的正常工作带来很大影响。在PCB 电路设计中,尤其在高频电路的PCB 设计中,必须防止地线的共阻抗所带来的影响。通过对共阻抗干扰形式的分析,详细介绍一点接地在电子电路中,特别是在高频电路中对共阻抗干扰的抑制作用,以及采用一点接地防止共阻抗应注意的问题。

同时对PCB 板内地线布局的主要形式和要求进行了简要阐述。

在电子电路中,多数元器件都要通过地线形成回路,线设计合理与否,直接影响电路的工作。尽可能地降低由于地线设计不和理产生对信号传输的干扰。

在电路图中,接地常用 符号来表示,表示电路中的零电位,并用来作为电路的其他各点的公共参考点。电路的各点电压、电流和信号电平的大小均是以地线作为基准电压来表示的。在阅读电路图和理解电路工作状态时,常把地线和各接地点之间视作无电位差的零电位点。而在实际电路工作中,由于地线的阻抗( 电阻、电感) 的存在,会产生一定的电位差。这些电位差的存在,必然对电路的工作带来影响。在PCB 设计中必须注意和消除地线阻抗的影响。

符号来表示,表示电路中的零电位,并用来作为电路的其他各点的公共参考点。电路的各点电压、电流和信号电平的大小均是以地线作为基准电压来表示的。在阅读电路图和理解电路工作状态时,常把地线和各接地点之间视作无电位差的零电位点。而在实际电路工作中,由于地线的阻抗( 电阻、电感) 的存在,会产生一定的电位差。这些电位差的存在,必然对电路的工作带来影响。在PCB 设计中必须注意和消除地线阻抗的影响。

1 地线对电路产生干扰的形式

1. 1 全电流共阻抗干扰

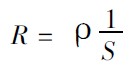

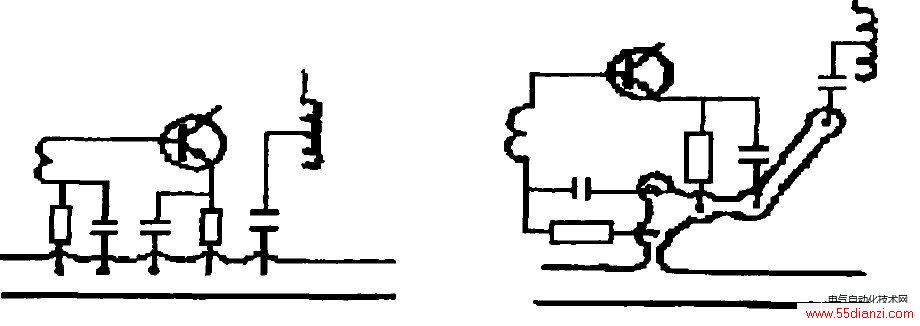

如图1 中,电路1 和电路2 通过公用地线AB与电源形成回路。线段AB 可等效为一个电阻和电感的串联回路,因而形成共阻抗效应。在工作时,电路1、2 的电流变动,将引起A 点电位变化,使电路1、2 相互产生干扰。如电路2 有输出至电路3, 干扰也将窜入电路3 中,因此形成全电流共阻抗干扰。

例如有一段长为10cm, 宽为1. 5cm 的印制导线,其铜箔厚度为50 微米,导线电阻为:

若ρ= 0. 02, 则R 约为0. 026Ω。当电路1 工作在低频时,电路的交变电流为1A, 则在这段印制导线上约产生0.026V 的交变电压降而作用在电路2上。在高频时,地线的共阻抗干扰,主要以导线的电感为主。当一段导线长度远大于其宽度时,导线的自感量可按0. 8 微亨/ 米计算。同样一段长10cm的导线,当其通过的工作频率为30MHz 时,此段导线所呈现的感抗RL= 2π L≈16Ω。可见在频率升高时,导线的感抗将比导线本身的电阻要大几个数量级。即使导线中流过很小的高频电流,如为10mA, 在导线上将产生0.16V 的高频电压。因而,对于高频电路,在制作PCB 时,印制导线要尽可能短,以减少导线感抗对电路带来的损耗与干扰。

图1 地线共阻抗干扰

1. 2 局部电流共阻抗干扰

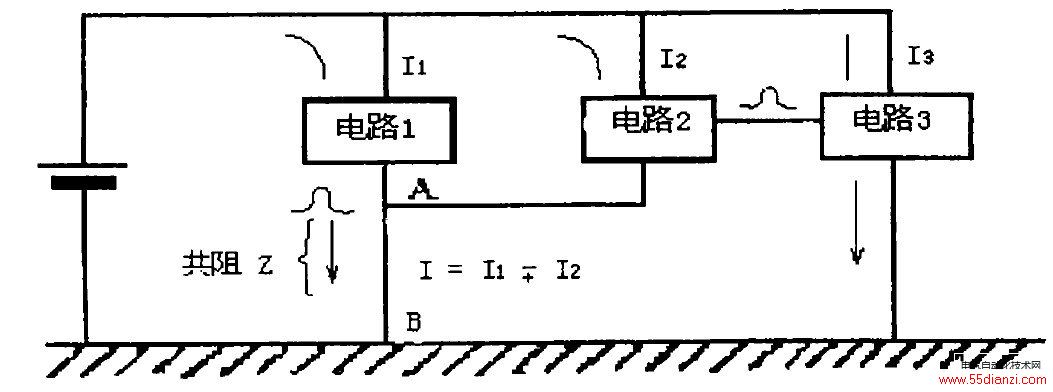

如图2 所示,当印制板采用环形地线,各接地元件按就近分散接地。这样末级的交流信号一部分通过地线AD 形成回路,在导线AD 上产生交流压降。

由于前级的晶体管发射极和基极与末级共用导线BC, 在导线BC 上产生共阻抗干扰。这种干扰是以局部电流的形式在公共地线上产生耦合,形成局部电流共阻抗干扰。

图2 另一种共阻抗干扰

全电流共阻抗干扰主要存在于级与级之间。局部电流共阻抗干扰则是指部分和个别元件与导线的接地点不良而对其他电路引起的干扰。

2 防止共阻抗干扰的方法

各级内部接地。各级内部接地是防止局部电流共阻抗干扰的主要方法。即有效地防止了本级的交流信号通过各接地元件而逸出至本级以外的电路中去,或其他电路的交流信号,通过本级的各接地元件而检拾进来。

无论对于低频、中频、还是高频各级电路,防止局部电流的共阻抗干扰,唯一有效的方法是采用一点接地。

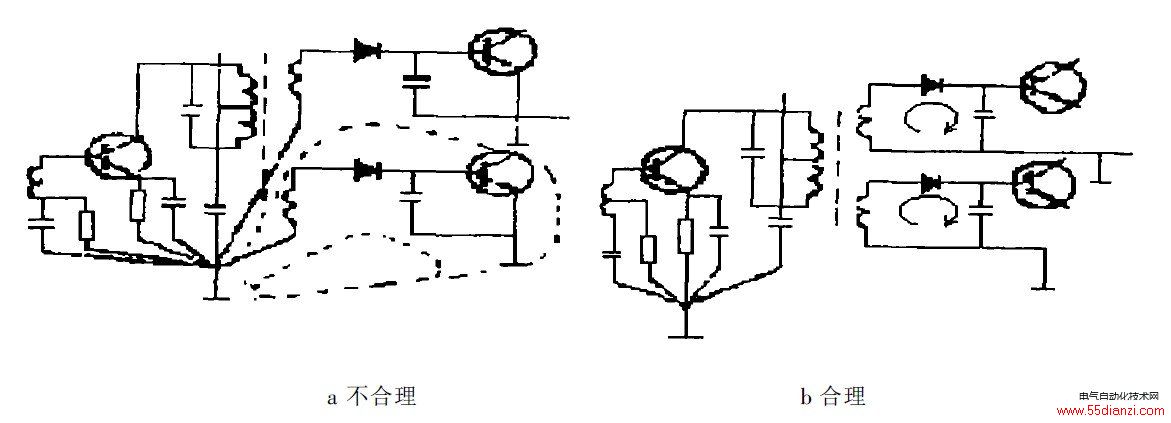

一点接地的形式如图3 所示。图中将各级内部的接地元件,即本级电路的发射极基极和集电极的所有接地元件,均安排在一个接地点上与地线相接。

这样,就能有效地防止交流信号通过接地元件的发散和接收,使接地纯净。

图3 一点接地

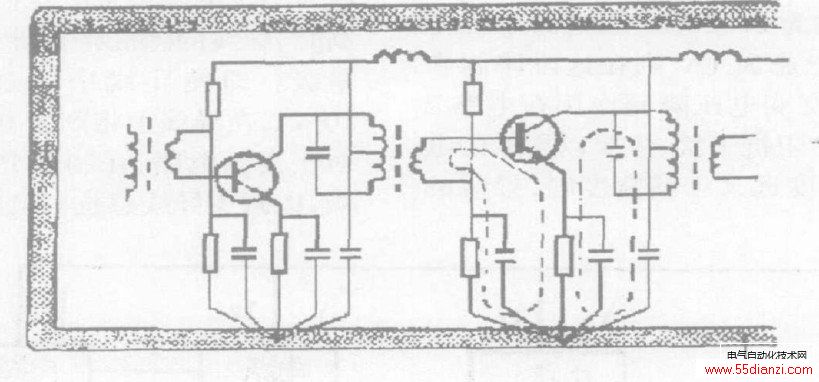

在实际电路中,各级的接地元件较多,不可能将这些元件同时穿入一个穿线孔内,而是将本级接地元件尽可能就近安排在公共地线的一段或一个区域内,如图4a 所示。有时遇到元件体积限制或排列上的原因,就近安排有困难时,可采用图4b 所示的接地形式,同样可达到一点接地的效果。

图4 排版中的一点接地

3 一点接地应注意的问题

3. 1 本级接地元件的范围

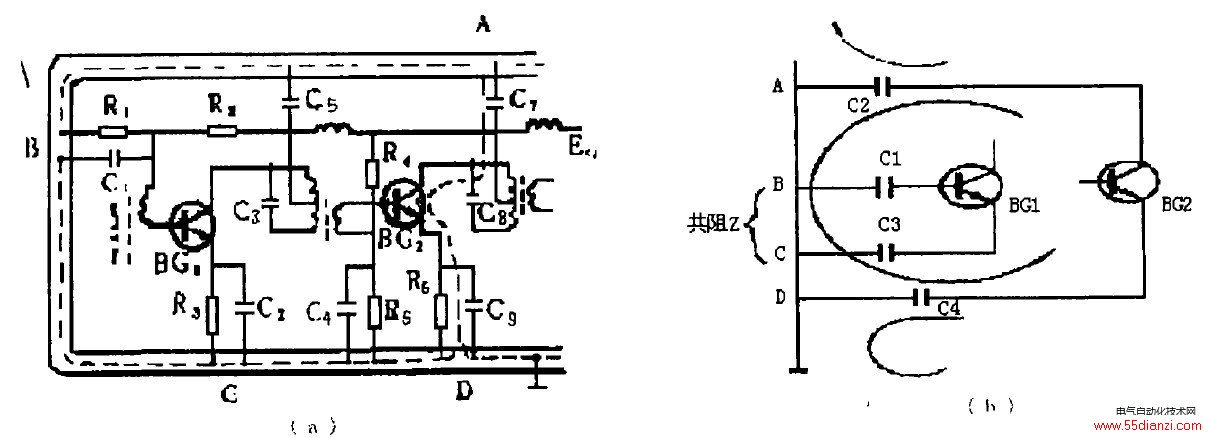

本级接地元件的范围是指与本级晶体管直接连接,或是通过电容耦合的元件。由电感耦合的次级及元件不属于本级。如图5a、图5b 所示。

图5 分组检波器的一点接地

3. 2 采用接地分支作一点接地

在元件不多、体积不大时,一点接地的布局比较好处理; 在元件较多,且体积较大时可采用较长的接地分支。在排版中也可以沿印制版周围布设,但不应使其他级的元件接入此接地分支上,接地分支的远端不应再和其他地线相接。

3. 3 一点接地也包括本级的板外元件在内

一点接地除了本级的板内元件外,还包括与本级直接或通过电容耦合的板外元件。这一点在PCB 设计中常被忽略,而造成局部电流的共阻抗干扰。

3. 4 高频电路的一点接地

高频电路的地线一般采用大面积覆盖接地,但这并不意味着各级内部元件的接地可以分散接地。

4 板内地线布局

印制版内地线是用来连接电路各级或各部分之间的接地的。板内地线布局,主要应防止各级和各部分之间的全电流共阻抗干扰。

4. 1 板内地线布局的要求

当板内的电路数量较多,地线的布局必须做到下列几点:

本文关键字:暂无联系方式电子技术,电工技术 - 电子技术

上一篇:鼠标与键盘常见故障排除方法