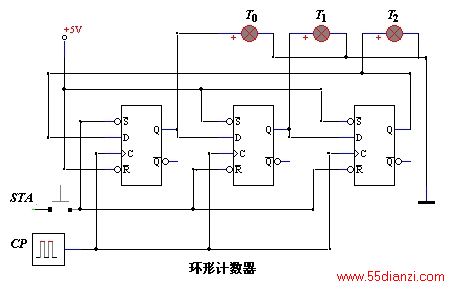

① 环形计数器电路结构

如图所示环形计数器电路,最高位触发器输出端 Q2

反馈到最低位触发器输入端

D0

。反馈函数是 D0

= Q2 。

环形计数器的有效状态是:100→010→001→100… 在连续时钟脉冲作用下,寄存器中的数据进行循环右移。因此,用寄存器输出不同状态对时钟脉冲进行计数,从这个角度来看,环形计数器可以作为非二进制计数器。但是在计算机和数字系统中常用做节拍发生器。

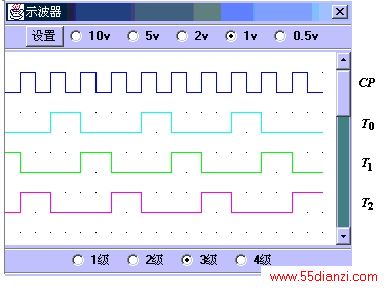

② 波形图

环形计数器工作时,首先用启动脉冲置入有效状态,然后才能加

CP。

3 个触发器组成的环形计数器构成 3 节拍发生器

T0 ~ T2 。若构成

n 节拍发生器,则需 n 位触发器,Tn = n。电路有效状态数是

n 个。

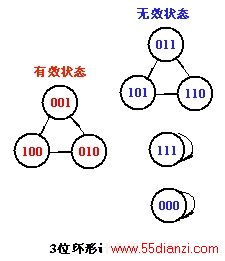

③ 状态图

下面是环形计数器状态图。有效状态

3 个,电路进入有效循环;无效状态

5 个,电路进入 3 个无效循环。电路运行时,由于某种干扰信号一旦进入无效循环之后,电路将不会自动返回有效循环中去,说明该环形计数器是不能自启动的电路。

④ 优缺点

环形计数器的突出优点是电路结构极其简单。而且,在有效循环的每个状态只包含一个 "1" 时,可以直接以触发器的状态表示节拍,组成节拍发生器,不需要另外加译码电路。

缺点是没有充分利用电路的状态。n 位触发器,电路总共有 2n 个状态,现只用 n 个状态。

本文关键字:计数器 电子技术,电工技术 - 电子技术

上一篇:最大长度移位寄存器