在数字电路中,常常需要将一些数码、指令或运算结果暂时存放起来,这些暂时存放数码或指令的部件就是寄存器。由于寄存器具有清除数码、接收数码、存放数码和传送数码的功能,因此,它必须具有记忆功能,所以寄存器都由触发器和门电路组成的。一般说来,需要存入多少位二进制码就需要多少个触发器。

寄存器中可分为数码寄存器(也简称为存器)和移位寄存器两种。它们共同之处是都具有暂时存放数码的记忆功能,不同之处是后者具有移位功能而前者却没有。

23.1.1 数码寄存器

数码寄存器的逻辑图如图10-1-1所示,它的存储部分由D触发器构成。

数码寄存器的工作原理

当接收脉冲CP的高电平到来后,输入数据X1~X4就并行存入寄存器。因为输入数据加于触发器的D端,数码若为“1”,D也为“1”。由D触发器的真值表可知,CP作用后,D触发器的输出端Qn+1=D n=1;若输入数码为“0”, Qn+1=D n=0。可见,不管各位触妆器的原状态如何,在CP脉冲作用后。输入数码X1~X4就存入寄存器,而不需要预先“清零”。

图23-1-1 数码寄存器

这种寄存器每次接收数码时,只需要一个接收脉冲,故称单拍接收方式。显然,从传送速度来看,单拍接收方式要快一些。在数字式仪表中,为了节省复位时间,往往采用单拍接收方式。

图23-1-1介绍的寄存器在接收数码时,各数码是同时输入到寄存器中去的。输出时也是各位同时输出的。因此,称这种输入、输出方式为并行输入并行输出。寄存器也可以用JK触发器构成,它的工作原理也很简单,在此就不再分析了。

23.1.2 移位寄存器

23.1.2.1 移位的概念

在数字系统中,常常要将寄存器中的数码按时钟的节拍向左移或右移一位或多位,能实现这种移位功能的寄存就称为移位寄存器。移位寄存器是数字装置中大量应用的一种逻辑部件,例如在计算机中,进行二制数的乘法和除法都可由移位操作结合加法操作来完成。

移位寄存器的每一位也是由触发器组成的,但由于它需要有移位功能,所以每位触发器的输出端与下一位触发器的数据输入端相连接,所有触发器公用一个时钟脉冲,使它们同步工作。一般规定右移是向高位移,左移是向低位移,而不管看上去的方向如何。例如一个移位寄存器中的数码是

高位 低位

原数据 1 0 0 1

右移:串出1 ¬ 0 0 1 X ¬ 串入

原数据 1 0 0 1

左移:串入 ® X 1 0 0 ®1串出

在移位的过程中,移出方向端口处触发器的数据将移出寄存器,称为串行输出,简称串出;在寄存器另一端口处的触发器将有数据X移入寄存器,称为串行输入,简称串入。如果连续来几个时钟脉冲,寄存器中是数据就会从串行输出端一个一个送出,于是可以将寄存器中的数据取出,同时有新的数据从串入端一个一个进入寄存器。从寄存器中取出数据还有另一种方式,前面已经提过,就是从每位触发器的输出端引出,这种输出方式称并行输出,简称并出,同理送入数据有并入的方式,见图23-1-1。

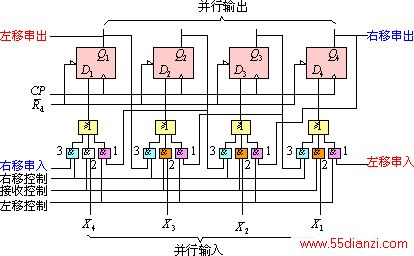

23.1.2.2 双向移位寄存器

此移位寄存器的各种功能各需要有一个控制端,即有左移、右移、接收数码三个控制端,这些功能都不执行即相当保持功能。需要说明的是左移、右移、保持和并行输入数据相当是一次信号,这些功能只能一个一个的进行。如果是高电平有效,那么左移、右移、保持和并行输入数据这些输入端,其中只能有一个是高电平,否则寄存器不能正常工作。

图10-1-3 双向移位寄存器

实现并行输入时,接收控制端为“1”,其化控制端为“0”,全部2号与门打开,在CP作用后,数据X1~X4就分别通过2号与门,并行送入各位触发器中。

实现右移时,右称控制端为“1”,其它控制端置“0”全部3号与门打开,3号与门的连线是按照右移功能的要求,从低位连向高一位的触发器。因此,CP脉冲作用后就实现右移。

实现左移时,左移控制信号为“1”,其它控制端为“0”,全部1号与门打开。通过1号与门的数据是按左移功能连接的。因此,在CP脉冲作用后就实现了左移。

至于,“右移”、“左移”以及“接收”三种控制信号,则是由另外的控制电路送来的。根据这些控制命令,移位寄存器在不同的时间内完成不同的功能。

寄存器的输出缓冲级往往采用三态门(TSG),这样,可以根据需要断开寄存器和外电路之间的联系,或者扩展寄存器的个数,或者将寄存器的输出端都接到同一条输出总线上,大大简化寄存器的外电路连接,使寄存器的应用更方便。集成化移位寄存器一般均设置时钟缓冲门。下面介绍一种常见的单块集成移位寄存器。

下面介绍几种移位寄存器电路,一般移位寄存器在应用中,需要有左移、右移、保持和并行输入数据等多种功能。。图23-1-2是一个双向移位寄存器,它可实现右移、左移、并入、并出、串入和串出等操作,即能右移又能左移,故称双向移位寄存器。

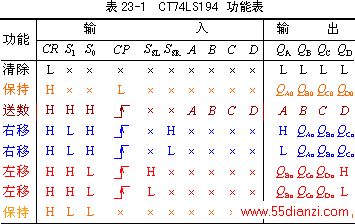

23.1.2.3 74LS194型通用多功能移位寄存器

74LS194的逻辑图符号见图10-1-3,这是一种具有并行输出、并行输入、左移、右移、保持等多种功能的移位寄存器。逻辑符号中的SRG4(Shift Register 4)是四位移位寄存器的缩写。

74LS194的功能表见表10-1,国标逻辑符号见图23-1-3。下面结合

74LS194的功能表和逻辑符号来说明该电路的逻辑功能。

1.清零

当清零端CR输入低电平时,各触发器全置“0”。进行其他操作时CR端均要处于高电平。

本文关键字:寄存器 电子技术,电工技术 - 电子技术

上一篇:译码器