译码器是典型的组合数字电路,译码器是将一种编码转换为另一种编码的逻辑电路,学习译码器必须与各种编码打交道。从广义的角度看,译码器有四类:

二进制码译码器,也称最小项译码器,N中取一译码器,最小项译码器一般是将二进制码译为十进制码;

代码转换译码器,是从一种编码转换为另一种编码;

显示译码器,一般是将一种编码译成十进制码或特定的编码,并通过显示器件将译码器的状态显示出来。

编码器,一般是将十进制码转换为相应的其它编码,其实质与代码转换译码器一样,编码是译码的反过程。

19.4.1 二进制码译码器

二进制码译码器又名最小项译码器,N中取一译码器。n为二进制码的位数,就是输入变量的位数,N=2 n,所以,N也是输出量的数目,或全部最小项的数目。因为最小项取值的性质是对于一种二进制码的输入,只有一个最小项为“1”,其余N-1个最小项均为“0”。所以,二进制码译码器也称为n线/N线译码器,例如对于三位二进制码译码器,可称为3线/8线译码器,这种称呼往往见于器件手册。

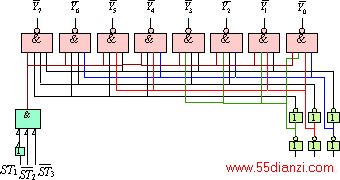

三变量二进制码译码器的逻辑图如图19-4-1所示,该逻辑图由三部分构成,译码器部分、输入缓冲部分和使能控制部分。该电路的简化逻辑符号如图19-4-2所示。

19.4.1.1 译码部分

码部分由图19-4-1中的八个与非门构成,最小项译码器如果用与门构成,则输出高电平有效;如用与非门则输出低电平有效。最小项取值的特点是N中取一,若输出高电平有效,则被选中的最小项为H,其余为L;若输出低电平有效,则被选中的最小项为L,其余为H。不论何种方式,都可以将被选中的最小项确定下来。译码逻辑式为

![]() 或

或 ![]()

![]() 或

或 ![]()

![]() 或

或 ![]()

![]() 或

或 ![]()

![]() 或

或 ![]()

![]() 或

或 ![]()

![]() 或

或 ![]()

![]() 或

或 ![]()

产品的3线/8线二进制译码器74LS138是低电平输出有效,即选中的二进制码,对应的输出只有一个“0”,所以译码逻辑式为以上右侧的一排。这里有一点需要注意,习惯上往往可以通过集成电路端口符号的标注,可以看出这个端口是低电平有效还是高电平有效。例如输出端标Y是高电平有效,正逻辑是“1”电平有效;如果标 ![]() 则是低电平有效,对正逻辑是“0”电平有效。这里要注意对端口的标注,Y和上面的反号应作为一个符号理解,

则是低电平有效,对正逻辑是“0”电平有效。这里要注意对端口的标注,Y和上面的反号应作为一个符号理解, ![]() 只说明该端口是低电平有效,不能理解为先得到Y再求反。至于定义高电平有效还是低电平有效,对电路的工作原理来说是一样的,N中取一个“1”,还是N中取一个“0”都可以完成对输入二进制码的译码。

只说明该端口是低电平有效,不能理解为先得到Y再求反。至于定义高电平有效还是低电平有效,对电路的工作原理来说是一样的,N中取一个“1”,还是N中取一个“0”都可以完成对输入二进制码的译码。

图19-4-1 三变量最小项译码器逻辑图

19.4.1.2 输入缓冲部分

输入缓冲部分见图19-4-1中右下方的六个非门,通过这六个非门可以获得三个输入变量的原变量和反变量。这样译码门的输入端就可以接到相应非门的输出端,而不必接到译码器的输入端。这样就可以减少信号源的负担,或者说,信号源接这样的译码器可以多接几个,而直接接到译码门上,就接不了那么多了。否则超出了信号源的电流(扇出)承担能力,信号源的逻辑电平就会超标,违反了双值逻辑系统的规定。

19.4.1.3 使能部分

对于三变量最小项译码器,例如74LS138,它的使能端是一个与逻辑,见图19-4-1的左下部分。“使能”(enable)的意思是使电路能不能工作,使能逻辑为

![]()

当 ![]() 时,使能输出为“1”,解除对译码门(与非门)的封锁,允许译码。当

时,使能输出为“1”,解除对译码门(与非门)的封锁,允许译码。当 ![]() 时,使能输出为“0”,禁止译码,即全部八个译码门的输出全部为‘1’。

时,使能输出为“0”,禁止译码,即全部八个译码门的输出全部为‘1’。

74LS138的功能表见表19-7。

表19-7 74LS138的功能表

输 入

输 出

本文关键字:译码器 电子技术,电工技术 - 电子技术

![]() B

B

上一篇:数码比较器