双极集成电路是指以通常的NPN或PNP型双极型晶体管为基础的单片集成电路。它是1958年世界上最早制成的集成电路。双极型集成电路主要以硅材料为衬底,在平面工艺基础上采用埋层工艺和隔离技术,以双极型晶体管为基础元件。

按功能可分为数字集成电路和模拟集成电路两类。在数字集成电路的发展过程中,曾出现了多种不同类型的电路形式,典型的双极型数字集成电路主要有晶体管-晶体管逻辑电路(TTL),发射极耦合逻辑电路(ECL),集成注入逻辑电路(I2L)。TTL电路形式发展较早,工艺比较成熟。ECL电路速度快,但功耗大。I2L电路速度较慢,但集成密度高。同金属――氧化物――半导体集成电路相比,双极型集成电路速度快,广泛地应用于模拟集成电路和数字集成电路。

双极型集成电路的特点是:工作速度高,易于做成大规模集成电路,功耗低等。双极型集成电路的两种形式:TTL集电极开路门(OC门)和三态门。

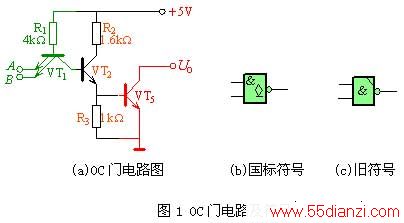

(1) OC门的工作原理

将TTL与非门中的VT3、VD4去掉,就得到集电极开路(Open Collector)门,如图1所示。由于VT5的上拉部分VT3、VD4去掉,VT5将不能得到高电平,为此OC门在工作时必须在输出端与电源之间接一个电阻,这个电阻称为上拉电阻。

由于上拉电阻的接入,又给OC门带来一些特点,主要是OC门的输出端可以并联。这在标准TTL系列的推拉式输出级是不允许输出端并联的,例如二个逻辑门的输出端并联,一个是高电平输出,另一个是低电平输出,因为处于开态的输出管电阻很小,从另一个门就会有很大的拉电流流出,灌入处于开态的输出管中。从而使输出低电平电压值超出规定的逻辑电平,最后门的输出即不是高电平,也不是低电平,在双值逻辑系统中出现这种情况是不允许的。

但是OC门可以将几个输出端连在一起,公用一个集电极负载电阻Rc,只要Rc的阻值大小合适,就可以限制电流的数值,电路就可正常工作。当然也可一个门单独使用。

(2)OC门的逻辑功能

OC门的特点是能实现“线与”功能,可以节省门数,减少输出门的级数,它可应用在数据总线上。当每个OC门只要有一个输入端为低电平时,OC门的输出均为高电平。

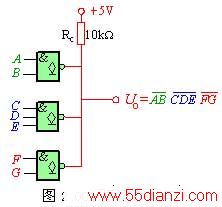

当几个OC门的输出端连在一起时,图2中给出了三个OC门连接的情况。门G1的输出

上述逻辑关系的获得,并不需要增添很多元件,只外接一个负载电阻即可,因而很方便、经济,同时OC门的功耗也有下降。但需注意,不是所有的与非门都可以在输出端实行“线与”。例如,前面介绍的标准TTL与非门就不能“线与”。

(3)集电极负载电阻的确定

RC的值大小合适,OC门连在一起才能正常工作。RC的数值可以在很大的范围之间选择,一般可以在1kW~100 kW。RC选取较小值,输出的上升沿较小;选取较大值,输出的上升沿较大,需要根据实际需要进行确定。

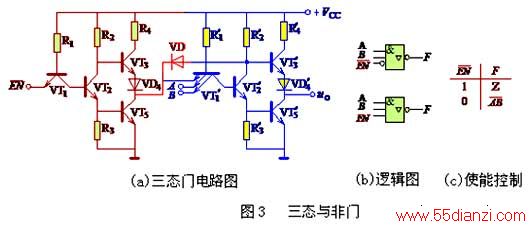

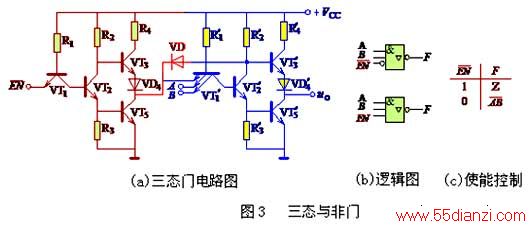

三态与非门与一般与非门不同,它的输出端除了可以出现高电平、低电平外,还可以出现第三种状态――高阻状态,或称禁止状态。

(1)三态与非门的结构和工作原理

图3(a)的右半部分就是一个与非门,左半部分是一个非门,非门的输入端是![]() ,

,![]() (Enable)称为使能端,在本电路中是低电平有效。当

(Enable)称为使能端,在本电路中是低电平有效。当![]() =0时,左侧的非门输出一个高电平给右侧的与非门。这时,二极管VD截止不起作用,右边的与非门将按照与非的逻辑关系把输入信号uI1和uI2传送到输出端,即当

=0时,左侧的非门输出一个高电平给右侧的与非门。这时,二极管VD截止不起作用,右边的与非门将按照与非的逻辑关系把输入信号uI1和uI2传送到输出端,即当![]() =0时,

=0时,![]() 。当

。当![]() =1时,应该是第三种高阻状态。

=1时,应该是第三种高阻状态。![]() =1使非门输出一个低电平给与非门,与非门的输入端有一个是低电平,这个低电平,应该使与非门输出高电平,即与非门输出级的VT′5是截止的。这时只要将与非门输出级的上拉部分截止,就可以获得VT′3和VT′5都截止的高阻状态。非门输出低电平,二极管VD导通,这时U′b3≈1V,所以VT′3和VD′4截止。这时从输出端看进去,VT′3、VD′4和VT′5均截止,电路处于高阻状态。

=1使非门输出一个低电平给与非门,与非门的输入端有一个是低电平,这个低电平,应该使与非门输出高电平,即与非门输出级的VT′5是截止的。这时只要将与非门输出级的上拉部分截止,就可以获得VT′3和VT′5都截止的高阻状态。非门输出低电平,二极管VD导通,这时U′b3≈1V,所以VT′3和VD′4截止。这时从输出端看进去,VT′3、VD′4和VT′5均截止,电路处于高阻状态。

因此我们把三态门按与非逻辑功能工作的状态叫作三态门的工作状态。左边的非门叫作三态门的控制部份,使能端可以是低电平有效,也可以是高电平有效,这在逻辑符号上有一些不同,见图18-3-3(b)。图18-3-3(b)上面一个是使能端![]() =0为工作状态;下面的一个是使能端EN=1为工作状态。图18-3-3(a)的电路对应的是使能端低电平为工作状态。

=0为工作状态;下面的一个是使能端EN=1为工作状态。图18-3-3(a)的电路对应的是使能端低电平为工作状态。

现行国标三态门的逻辑符号,在输出端边框线内侧加一个等边三角形,一角向下。EN为使能端,有空心小圆者,代表EN低电平使能;无空心小圆者,代表EN高电平使能。高阻状态常用字母Z表示。

(2)三态门的应用

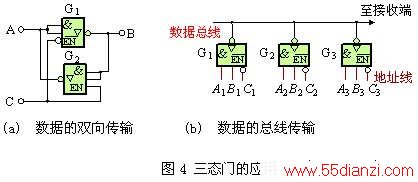

三态门在数字电路中是一种重要的器件,它大多挂接在一组总线(Bus)上,以实现不同数字部件之间的数据传输,见图4。

图4(a)的电路可实现数据的双向传输,当控制端C=0时,三态门G1工作,G2高阻,数据由A传输到B。当C=1时,G2工作,G1高阻,数据由B传输到A。图4(b)是数据的总线传输方式,若干个三态门挂在一条传输线上,其中一个是工作状态,其余的是高阻状态,这样数据就可以向接收端传输。这些三态门采用分时的工作方式,可以使用同一条传输线传输数据。如果这些三态门具有双向功能,每一个三态门既可以发送数据,也可以接收数据。

三态门的特点是输出端除了高电平、低电平两种状态外还有第三种状态:高阻状态或禁止状态。

本文关键字:集成电路 电路基础知识,电子学习 - 基础知识 - 电路基础知识

上一篇:铜连线技术