近几年有不少刊物载文介绍用多片低分辨率A/D及D/A转换器芯片组成高分辨率A/D转换器,但也有少数作者著文提出异议,认为上述方法可论而不可行。对此,我们略有同感。那么,当遇到实际情况需要进行高分辨率A/D转换,且环境要求较荷刻的场合时,如油井探测、地震数据采集、轻型工业秤及其他高精度测试仪器等,究竟该如何处理呢?本节介绍一种低功耗、高性能的16位A/D转换器ADC1143及其与80C31单片机的接口,作为解决上述问题的方法之一。

一、ADC1143的主要特性

●16位高分辨率。

●转换时间:ADC1143J最长转换时间为70 μs;ADC1143K最长转换时间为100μs。

●带参考电源和时钟脉冲。

●低功耗:

当Vs=±15 V时,最高功耗为175 mW;

当Vs=±12 V时,最高功耗为150 mW。

●最大非线性:ADC1143J为±0.006%;

ADC1143K为±0.003%。

●动态非线性温度系数:ADC1143J最大为±2×10-6/℃;

ADC1143K最大为±l×10-6/℃。

●无误码(0~+50℃):13位(ADC1143J);

14位(ADC1143K)。

●供电范围:Vs=±11.4~±18.0 V;

VD=+3.0~+18.0V。

二、ADC1143的内部结构和引脚功能

1.内部结构

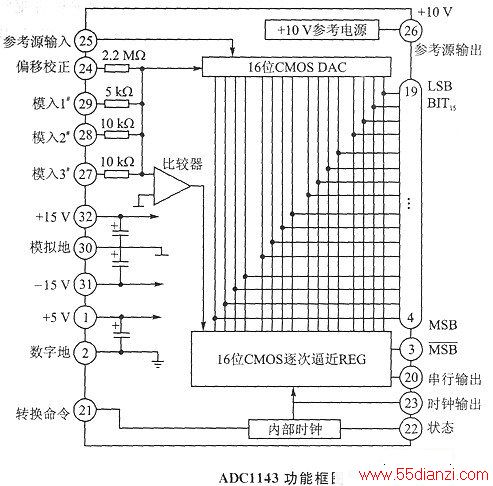

ADC1143是一种逐次逼近型A/D转换器,主要由16位CMOS DAC、16位逐次逼近寄存器、低功耗比较器、内部时钟、低噪声参考电源以及模入电阻网络和高质量旁路钽电容等组成。16位的CMOS DAC包括薄膜电阻和电流控制开关等模拟器件。ADC1143正是利用了CMOS电路和薄膜组件,才使其获得了低功耗、高精度和小尺寸等优越性能。ADC1143的功能框图如图1所示。

2.引脚功能

ADC1143共有32个引出脚,被封装在约(51×51×10.4)mm3的芯片内。32个引脚分两排放置。

现将有关引脚功能分述如下(参见图1):

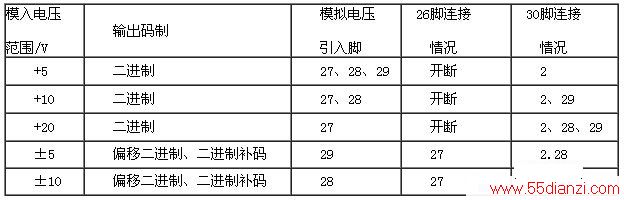

①模人电压引脚(27~29脚):模入电压范围可编程,其编程情况见表1。

模拟输入范围引脚编程表:

②参考电源输入、输出脚(25脚和26脚):使用内部参考源,将25脚与26脚之间接100 n精密电位器,以进行增益校准。当使用外部参考源时,要如图2所示连接。

③偏移校正引脚(24脚):零输出校正用。

④并行数据输出引脚(4~19脚):具有数据锁存功能,无三态驱动,以偏移二进制码输出。

⑤MSB(3脚):二进制补码输出使用位。

⑥模拟地和数字地(30脚和2脚):模拟地和数字地在ADC1143内没有连接。因此,在组成系统时,要通过外部连接,以一点连接为最佳。

⑦状态引脚(22脚):反映ADC1143的工作状态的信号。

⑧转换命令引脚(21脚):用于启动ADC进行A/D转换,该脚信号的下降沿,各内部状态全部复位。

⑨其他引脚从图1可顾名思义或一目了然,不再一一叙述。

二、ADC1143的工作过程

ADC1143的工作过程可以通过图3-106的工作时序图来说明。当被转换的模拟信号送到模入端后,便可启动A/D转换。启动转换脉冲是一个正脉冲,在该脉冲的下降沿启动转换,要求转换脉冲宽度至少要有1 μs。一旦启动转换,在转换结束之前就不能再发启动脉冲;否则,前次转换无效。转换命令脉冲的下降沿,所有内部逻辑都被复位,MSB被置高电平,其余位被置低电平,状态线也被置低电平,并保持到整个转换周期结束。

在转换期间,每位(从MSB开始)依次被内部时钟的上升沿置为高电平,ADC的内部DAC输出与当时的模拟输入电压比较,以确定该位的逻辑输出状态。当模人大于或等于DAC输出时,该位为1,否则为O。这样依次逐位进行比较,每一比较持续一个时钟周期。在状态线的上升沿并行输出数据有效。串行输出有效则是在每个确定位状态时钟周期的末尾。若不再启动转换,ADC1143的并行输出将保持有效,而串行输出有效仅保持一个时钟周期。

三、ADC1143与80C31的接口

作为成功应用ADC1143的一个实例,这里介绍笔者研制的某磁信号处理器中ADC1143与80C31接口的实现,其接口部分如图3- 107所示。图中将信号的放大、整理、保持以及数据输出和80C31的外部程序存储器等电路省去,旨在说明ADC1143的使用方法。

80C31是8031单片机的CHMOS型。它集成度高,速度快,备有空闲和掉电工作方式,可有效地降低电源消耗,如正常操作5V、16 mA;空闲方式5V、3.7 mA;掉电方式2V、50nA。而掉电和空闲方式都由软件控制实现。选用80C31是为配合ADC1143的低功耗,适合在便携式仪器、干电池供电的场合使用。若不如此,则可改换为8031即可,ADC1143输出逻辑与CMOS和TTL兼容。

由于ADC1143输出不具备三态功能,因此,其输出要经过74HC244驱动后,才能与80C31数据线(Po口)挂接。启动命令由Pl.6位控发出。转换结束的判断采取查询方式;若须采用中断方式,只须将状态信号经一级反相后再接P3.2(INTO)即可。由P2.5(A13)、P2.4(A12)和P3.7(RD)通过2个“或“门分别选通高位74HC244。从图3-107中可以看出,满足A/D高8位选通的条件是A+RD+A3=0,即读数地址为DFFFH;满足A/D低8位选通的条件是百+RD= A12 =0,即读数地址为EFFFH。

图中W1和W2分别完成ADC1143的偏移校准和增益校准,模人电压范围被编程为±10 V。在校准偏移时,要使得模入端为-9. 999 847 V,调整Wl,直至偏移二进制在00...0与00...1之间交换;在校准增益时,要使得模入端为+9, 999 54 V,调整W2,直至偏移二进制码在11... 10与11...11之间交换。

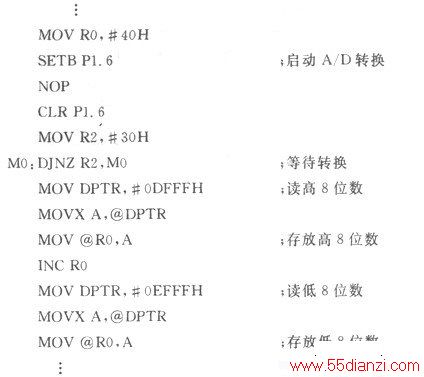

由上分析不难编写数据采集部分的程序。现设A/D转换数据按高、低8位分别放在80C31的40H和41H单元,并考虑转换等待时间。其程序段如下:

ADC1143性能优良,若用于一般的工业控制设备中会显得大材小用;但当用于高精度数据采集系统,如本节开头所提及的一些高精密、便携式测试仪以及其他计量设备时,ADC1143确有它恰到好处的优越性。