摘要:提出了一种新颖的CMOS四象限模拟乘法器电路,该乘法器基于交叉耦合平方电路结构,并采用减法电路来实现。它采用0.18μm CMOS工艺,使用HSPICE软件仿真。仿真结果显示,该乘法器电路在1.8 V的电源电压下工作时,静态功耗可低至80μW,其线性输入范围达到0.3 V,-3 dB带宽可达到1 GHz,而且与先前低电压乘法器电路相比,在同样的功耗和电源电压下,具有更好的线性度。

关键词:CMOS模拟乘法器;低压;高线性;减法电路

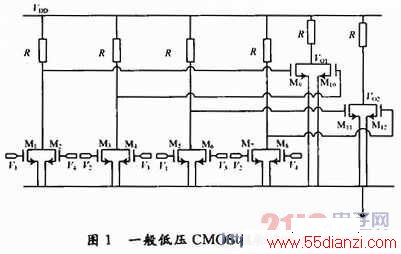

四象限模拟乘法器是模拟信号处理系统中的重要组成单元,它被广泛地应用于锁相环、频率变换、调制与解调、自适应滤波等许多模拟信号处理电路中。目前,适应于低压工作的CMOS四象限模拟乘法器由6个级联的两输入组合结构单元(Combiner)组成,这种结构已广泛应用于射频电路中,它的NMOS管分别对源漏相接,且通过负载电阻R直接到电源。因它的输入电压可直接控制晶体管电流,因而该乘法器工作所需要的电源电压很小,其最小的电源电压是NMOS栅源电压与负载电阻上的压降之和。但是这种乘法器结构含有较多的电流支路,电阻也相对较多,一定程度上增加了版图的面积和功耗,最重要的是该结构对MOS管的匹配有严格要求,否则线性度很难保证,这样也就对制造工艺提出了较高的要求。针对这一缺点,本文提出了一种新型模拟乘法器结构,它采用减法电路来提高电路的线性度。

1 电路工作原理

1.1 设计思路

图1给出适应于低压工作的CMOS四象限模拟乘法器结构(Cornbiner)。它的输出电压为:

输出电压:

![]()

式中:V1=Vx+v1;V2=Vx-v1;V3=Vy+v2;V4=Vy-v2;Vx,Vy是共模电平,v1,v2是差模电平;KN是晶体管的跨导参数;VTN是NMOS的阈值电压。

本文提出的新型模拟乘法器结构基于MOS管工作在饱和区的平方律特性实现了乘法运算,不仅省去图1所示乘法器电路中的多个电阻,也减少了电路的面积和功耗,最重要的是降低了晶体管对匹配的严格要求,因此可以提高电路的线性度。

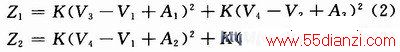

图2所示为该乘法器电路的设计框图。由图可知,

不管A1,A2,A3,A4是常数或者与输入信号有关,假设A1=A2=A3=A4,Vidl=V1-V2,Vid2=V3-V4,最后的差分输出:

![]()

这样最终就实现了乘法运算功能。

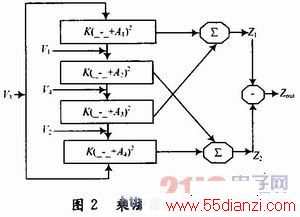

由图3可知,Vz与Vx之差就是Mx管的栅源电压,而且Mx管的栅源电压大小与输入电压Vy有关。假设Mx管与My管参数一样,有:

这里VTP是PMOS的阈值电压。由式(2)与式(3)相减,得:

将这种减法电路和4个工作在饱和区的NMOS管相结合,得到一种新型的CMOS四象限模拟乘法器,如图4所示。

/2011.01/17/14.jpg)

如上述,定义图4中2个差分输入对分别为Via1=V1-V2;Vid2=V3-V4,输出端Vo1,Vo2。为了使电路工作在饱和区,最小的电源电压必须满足:

![]()

式中:VEFFP为PMOS管的饱和压降。

对于深亚微米级CMOS工艺,一般PMOS管的阈值电压绝对值可低至0.6 V以下,因此只要合适选择晶体管尺寸,电路工作的电源电压可低至1 V。

利用式(7),输出端Vo1,Vo2的输出电压:

最终输出Vo,由式(6)、式(7)相减可得:

由输出式(11)可知,该乘法器的输出增益仅由负载电阻R,以及M9~M12晶体管的跨导参数决定。相比图1所示电路结构,节约4个电阻,减少了版图面积,电路结构更为简单。

2 电路仿真与分析

对图4所示乘法器使用HSpICe仿真软件进行仿真,其中MOS晶体管模型参数由典型0.18 μm CMOS工艺提供。电源电压为1.8 V,仿真结果显示,在1.8 V的工作电压下,该乘法器静态功耗可低至80μW,其线性输入范围达到±0.3 V,-3 dB带宽可达到1 GHz。

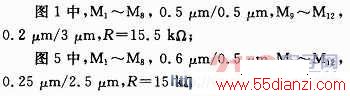

为合理比较图1和图4所示两种乘法器性能,将它们静态功耗和转换增益设为一致。晶体管参数设置如下:

其中2个电路静态电源功耗均设为195μW;图1中,Vid1,Vid2的共模电平设为0.66 V;图4中,Vid1的共模电平设为0.6 V,Vid2的共模电平设为0.2 V。

www.55dianzi.com

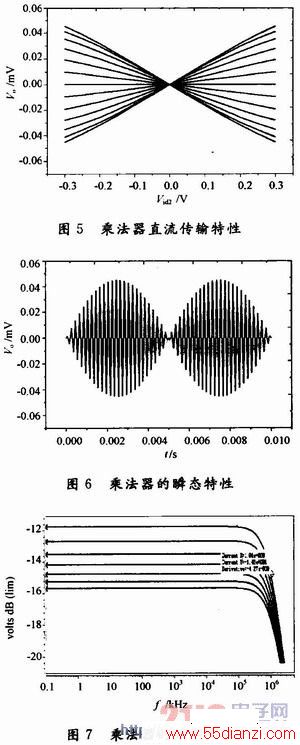

如图5所示:Vid1=±0.3 V,Vid2的输入范围也是-0.3~+0.3 V,且以50 mV的步长变化。可以看到对于整个输入动态范围,电路保持很好的线性度。

图6所示该乘法器用作调幅电路。在Vid1端输入一个幅值0.3 V,频率5 kHz的正弦载波信号,Vid2端输入一个同样幅值,频率100 MHz的正弦调制信号,得到一个完整的正弦包络。

如图7所示:固定V2,V3,V4输入不变,对V1以0.05 V步长进行DC扫描,扫描范围0.45~0.75 V。得到的-3 dB带宽为1 GHz。可见,图4所示乘法器频率特性良好,带宽较宽,可以处理较高频率信号。

图8是该乘法器电路THD仿真结果;图4中在Vid2加上频率100 kHz,幅度变化的正弦信号,Vid1固定在0.6 V;图1中在Vid2加上频率100 kHz相同幅度变化的正弦信号,Vid1固定在0.6 V,图中折线①代表图1乘法器的仿真结果,折线②代表图4乘法器的仿真结果,可以明显看出,对于同样的输入,图4所示乘法器失真更小,线性度更好。整体来说,本乘法器较好的完成了对模拟信号的相乘处理功能,在整个线性输入范围内都表现出完好的线性相乘结果,较高的线性度以及较大的-3 dB带宽,并经仿真验证成功,可能存在的不足之处在于其线性输入范围有待进一步提高。

本文关键字:暂无联系方式运算放大器,单元电路 - 运算放大器