计数器是典型的时序逻辑电路,它是用来累计和记忆输入脉冲的个数。计数是数字系统中很重要的基本操作,集成计数器是最广泛应甩的逻辑部件之一。计数器种类较多,按构成计数器中的多触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器;根据计数制的不同,可分为二进制计数器、十进制计数器和任意进制计数器;根据计数的增减趋势,又分为加法、减法和可逆计数器。还有可预置数和可编程序功能计数器等。下面以中规模集成电路计数器74LS192为例说明计数器在数字系统定时和产生时序脉冲方面的应用。

1 定时

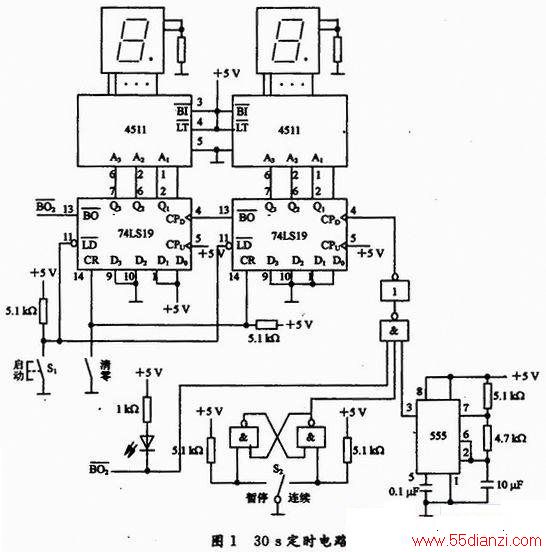

在下述例子中,要完成30 s递减计时,并具有显示功能,当计时器递减计数到零时,数码显示器显示为“00”,同时发出光电报警信号,系统设置外部操作开关,控制计时器的启动/复位和暂停/连续功能。如图1所示,计数电路选用两片中规模集成电路74LS192进行设计,74LS192是十进制计数器,具有“异步清零”和“异步置数”功能,且有进位和借位输出端。

两片74LS192构成预置数的三十进制递减计数器,计数器10位接成三进制;计数器个位接成十进制,置数端D3~D0通过开关接高低电平,若接高电平可进行其他置数;此计数器预置数为(0011 0000)2=(30)10,只有当低位端发出借位脉冲,高位计数器才做减计数。1片74LS192构成1 s减计数电路(即个位)。它的计数原理是:使高、低位加计数脉冲信号引脚CPU=1,计数脉冲由555组成的多谐振荡器产生,计数脉冲加入个位74LS192引脚CPD脚;当减计数到零时,74LS192的端发出借位脉冲,使十位计数器减计数;当高、低位计数器处于全零时,高位计数器74LS192的借位输出靖有效,即可实现报警。

该电路还可进行清零、置数,并通过接一与非门对555脉冲发生器输出靖的脉冲信号进行控制,即可实现对整个电路进行暂停计时,为减小开关按键产生的机械抖动对计时电路的影响,应接一RS锁存器;当计时器74LS192的借位输出端有效时,即可实现报警。最终计数器的输出通过CD4511七段译码器,并直接驱动半导体数码显示器显示。

可以看出,此电路用件少,分块清晰,采用按键操作,非常实用,可用作球类比赛的计时器。

2 顺序脉冲发生器

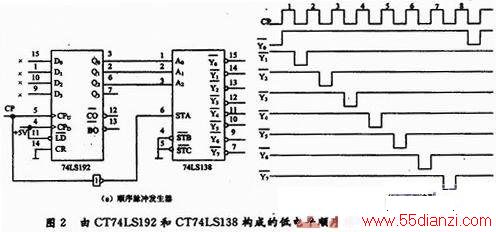

图2(a)所示为同步十进制可逆计数器74了LS192和输出低电平有效的3-8线译码器CT74LS138构成的顺序脉冲发生器。由于74LS192输出Q2,Q1,Q0的状态000~111循环变化,因此,它可作为译码器CT74LS138的三位二进制代码输入,分别与A2,A1,A0对应相连。这时电路在输入计数脉冲CP作用下,译码器的依次输出低电平顺序脉冲,如图2(b)所示。

为了防止产生竞争冒险现象,这里将计数脉冲经非门反相后作为选通脉冲![]() 接到CT74LS138的使能端STA上来控制译码器的工作。当输入计数脉冲CP的上升沿到来时,计数器进行计数,与此同时,非门输出

接到CT74LS138的使能端STA上来控制译码器的工作。当输入计数脉冲CP的上升沿到来时,计数器进行计数,与此同时,非门输出![]() 使STA为低电平0,译码器被封锁而停止工作,

使STA为低电平0,译码器被封锁而停止工作,![]() 输出高电平。

输出高电平。

当CP下降沿到来后,![]() 为高电平1,这时STA=1,译码器工作,相应输出端输出低电平。由上分析可看出,选通脉冲

为高电平1,这时STA=1,译码器工作,相应输出端输出低电平。由上分析可看出,选通脉冲![]() 使译码器工作时间和计数器中触发器的翻转时间错开了,从而有效地消除了竞争冒险现象。

使译码器工作时间和计数器中触发器的翻转时间错开了,从而有效地消除了竞争冒险现象。

3 结语

通过以上应用实例表明,计数器在数字电路中不仅在定时方面起着重要作用,在其他方面也有很高的应用价值。在电子技术的学习中,只要深入了解器件的工作原理和各种器件之间的相互关系,就一定能发现更多奥秘,给大家学习和工作带来更多的方便和帮助。

本文关键字:计数器 数字逻辑电路,单元电路 - 数字逻辑电路