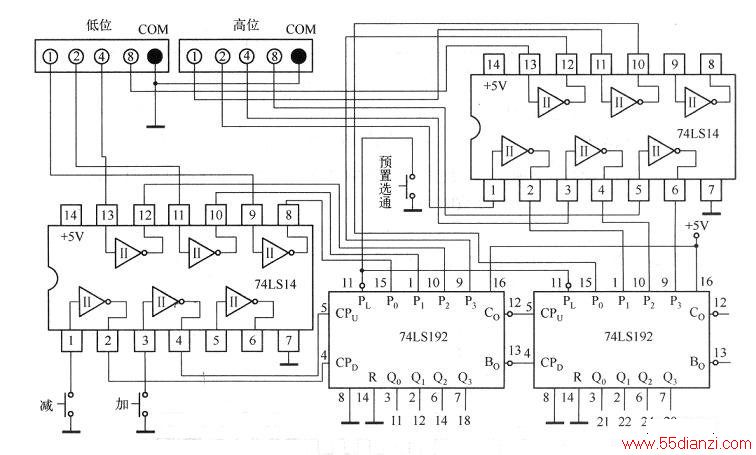

在图中,1V以下的计数器74LS192的时钟可以由“+”、“-”两键分别控制输出电压步进增减,1V以上的计数器74LS192的加、减计数时钟则由低位的进、借位输出提供。

如果需要3位以上的减计数和预置数,则可以在图中的基础上继续级联192、相应的拨码开关及相应的74LS14,直到满足要求为止。

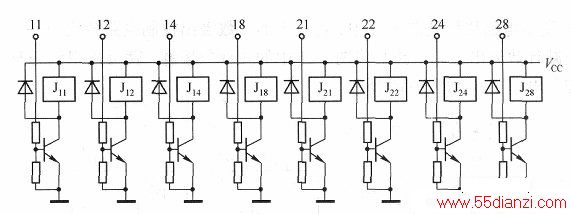

74LS192的输出接驱动继电器激磁线圈的晶体管基极,如下图所示。

为了使晶体管与TTL电平匹配,需要在74LS输出与晶体管基极之间串联适当的电阻,如15~20kΩ的电阻,同时在晶体管基极与发射极之间并联lOkΩ的电阻,以确保在74LS192输出低电位时晶体管处于关断状态。

上一篇:一种简单的逻辑笔电路