2.如何设计出最简的激励函数形式

由于选取的CP信号对应不变的状态有的没有脉冲的到来,这样的话,不管触发器的输人为何值,没有脉冲的触发状态就不会改变,设计的时候将该状态视为"无关项",可以使设计的激励函数更简单。

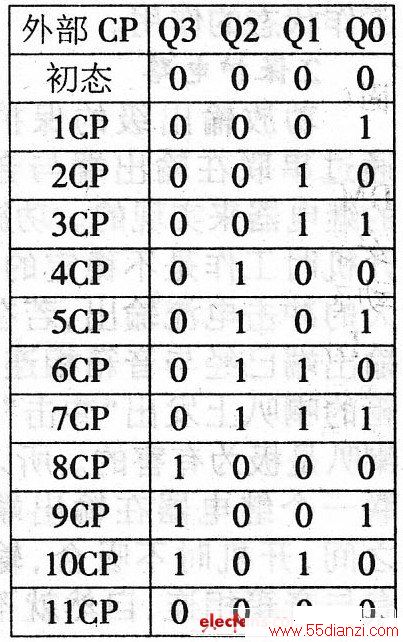

下面以11进制计数器为例。设计11进制计数器至少需要4个触发器,其状态对应为Q3 Q2 Q1 Q0,附表为11进制计数器简化的状态表。相邻的两行:上一行为下一行的"现态",下一行为上一行的"次态".根据附表可以比较容易完成设计的第一步:为每个触发器选取CP脉冲(假设触发器为下降沿触发)。

Q3触发器时钟信号CP3的设计:先观察Q2,发现Q3状态发生"0"到"1"的变化时,Q2有下跳脉冲,但Q3发生"1"到"0"的变化时Q2不变,故Q2不能作为Q3角虫发器的时钟信号;往前观察Q1,Q3的两次变化,Q1均有下跳脉冲,故CP3=Q1。

Q2触发器时钟信号CP2的设计:先观察Ql,Q2的两次状态变化(外部4CP时,Q2从 "0" 变"1";8CP时,Q2从"1"变"0")均对应Q1有下跳触发,故CP2=Q1。

Q1触发器时钟信号CP1的设计:当外部来了11CP时,Q1从"1"变"0",但Q0没有对应的下跳脉冲,故只能选取外部时钟信号作为CPI,即CP1=CP.Q0触发器的CP0=CP。

若选用的触发器为上升沿触发的话,只要选用对应触发器的Q作为CP信号。

选取好每个触发器的时钟信号后,开始设计触发器的激励函数:根据附表及触发器的CP脉冲信号,画出各触发器的"次态"卡诺图,得出"次态"方程,再根据所选触发器的类型,得到激励函数。

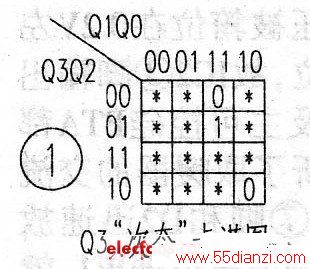

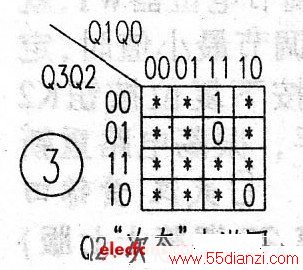

Q3的"次态"方程:从附表可以看出,Q1作为CP3共有3次下跳触发,分别的"现态"是0011、0111、1010时,对应Q3的"次态"依次为"0"、"1"、"0",填人图1.其他状态由于没有CP脉冲的触发,在图1的卡诺图中不管填人"0"还是"1",状态维持不变,可视为"无关项",以便于得到最简的"次态"方程。另外1011-1111为真正的"无关项".根据图1,Q3n+1=Q2.

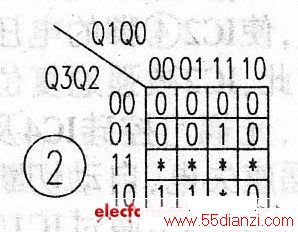

若选CP3=CP的话,则每个状态都有触发脉冲的到来,故其"次态"卡诺图如图2所示,得出的方程要复杂些。

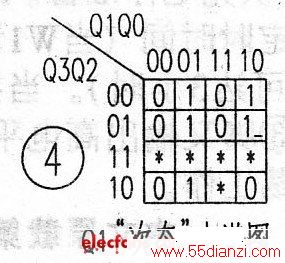

Q1的"次态"方程:CPI=CP,每个状态都有触发脉冲的到来,"次态"卡诺图如图4所示,Qln+1=Q0Q1+Q3Q0Q1.

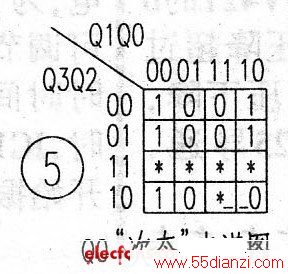

Q0的"次态"方程:CP0=CP,"次态"卡诺图如图5所示,Q0n+1=QlQ0+Q3Q0.

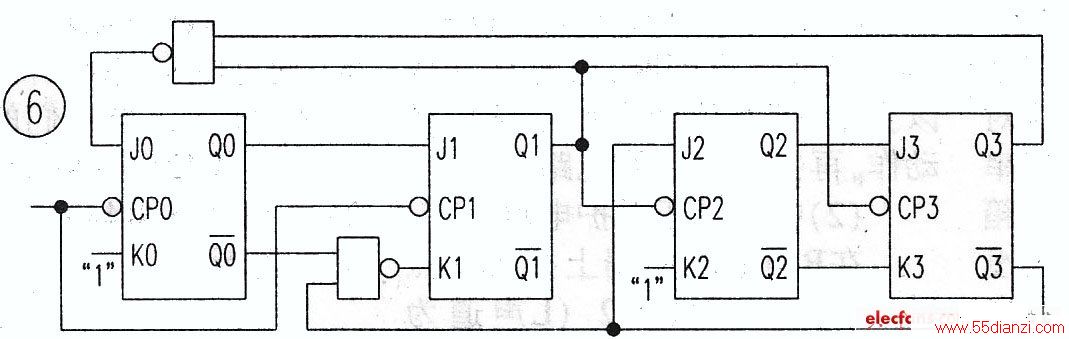

若使用JK触发器,将上述各"次态"方程与JK触发器的特性方程Qn+1=JQ+KQ进行比较,得出各·触发器的驱动函数:J3=Q2,K3=Q2;J2=Q3 ,K2=1;J1=Q0 ,K1=Q3 Q0;JO=Q3 Q1 ,KO=1.

最后检查发现电路具有自启动能力。画出逻辑电路,见图6.

本文关键字:计数器 数字逻辑电路,单元电路 - 数字逻辑电路

上一篇:显示译码器作用及类型