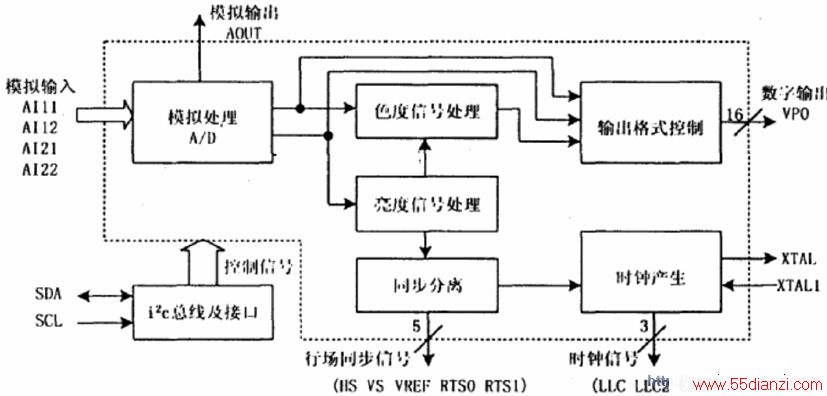

SAA7111A的功能方框图如图1所示。

从SAA7111A的四个模拟输入端AI11,AI12, AI21, AI22输入的视频图像信号,经模拟处理后 ,一路经A/D转换器后产生数字色度信号和亮度信号,分别进行亮度信号处理和色度信号处理。亮度信号处理的结果一路送到色度信号处理器,进行综合处理,产生Y和UV信号,经格式化后从VPO(16位)输出;另一路进入同步分离器,经数字PLL产生相应的行和场同步信号HS和VS,同时PLL驱动时钟发生器,产生与HS锁定的时钟信号LLC和LLC2。所有这些功能均是在I2C总线控制下完成的,其中SCL为串行时钟信号,SDA为串行数据信号。

SAA7111A的主要特点如下:

・ 可编程选择四路视频输入的一路或两路,组成不同的工作模式,在其内部有两路模拟视频信号处理通道,可进行静态增益控制或自动增益控制,还有两路模数转换器;

・ 可对芯片编程进行自电平控制、抗混叠滤波、梳状滤波;

・ 能实现行场同步信号的自动检测和分离,并且行同步信号的起始位置与结束位置均可根据需要进行编程控制,片内产生的时钟通过数字PLL锁定行同步;

・ 场频50Hz或60Hz自动检测,并在PAL和NTSC制之间自动切换;

・ 能对不同输入制式的亮度信号和色度信号进行处理,并实现亮度、色度和饱和度的片内控制;

・ 提供两种数据方式供选择,这两种数据方式分别是RGB和YUV,可灵活输出不同的数字图像数据格式,主要有:4:1:1的YUV格式(12bit ), 4:2:2的YUV格式(16bit), 4:2:2的YUV格式[CCIR-656](8bit), 5:6:5的RGB格式(16bit)和8:8:8的RGB格式(24bit);

SAA7111A在 实时图像 采集 系统中的应用

实时图像采集系统

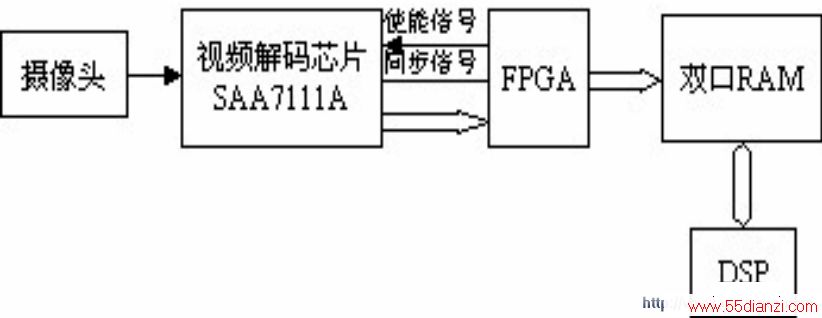

我们所设计的实时图像采集系统框图示于图2。

图2

实时图像采集系统主要包括视频解码芯片SAA7111A、FPGA及双口RAM。系统采集的实现框图如图2所示,视频解码芯片SAA7111A从输入的标准视频信号中分离出场同步信号、行同步信号、奇偶场信号、像素时钟信号,并按像素逐点输出4:2:2的YUV格式的数字图像数据。该格式中,图像的分辨率为720×576,即每行有720个像素点。再将这些场同步信号、行同步信号、奇偶场信号、像素时钟信号以及DSP的定时器送来的启动采样信号送给FPGA,利用其所具有的在线可编程的特点,产生指定的地址信号,FPGA根据这些信号,控制对当前场中图像的某一区域进行采集,并产生指定的地址送给双口RAM,将采集得到的图像数据写入双口RAM中进行缓存(如果当前场为奇数场,FPGA控制将采集的图像数据写入双口RAM中的RAM1存储域中;否则,当前场为偶数场,FPGA控制将采集的图像数据写入双口RAM中的RAM2存储域中)。当采集完毕后,FPGA中断(当前场为奇数场时,发中断4;否则,发中断5)给DSP,通知DSP可以开始对图像进行处理了,此时,DSP读取当前场采集得到的图像数据,和前一场中采集得到的图像数据进行放大、锐化的处理。

www.55dianzi.com

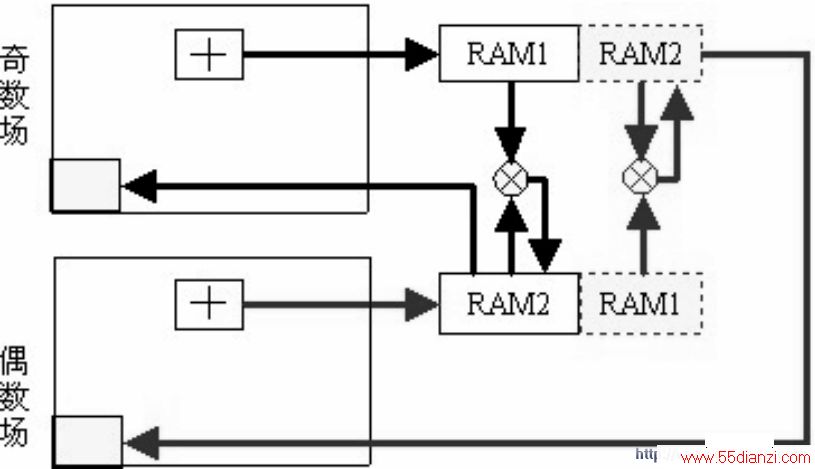

图3

模拟视频输入及时钟电路

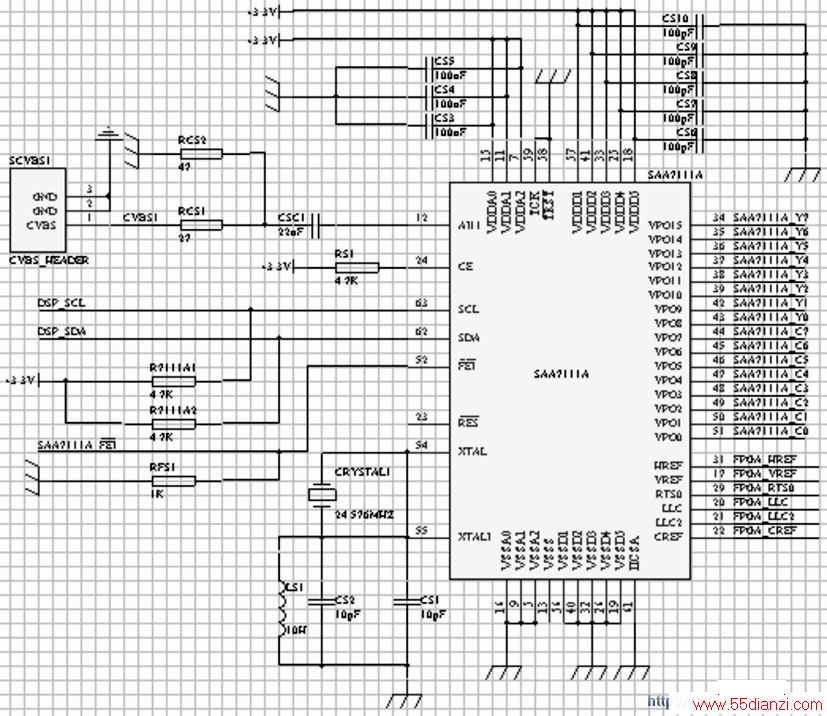

SAA7111A的模拟视频输入及时钟电路如图4所示。通过I2C总线设定地址为02的寄存器中的MODE2, MODEI, MODEO三个控制位的值,选择特定的工作模式。本系统工作在第一类工作模式的第 一种,即从SAA7111A的四个模拟视频输入端中选择AI11作为视频输入接口,输出亮度和色度。信号在视频输入端需要连接22nF的电容和阻值分别为27和47欧姆的两个电阻。

图4

SAA7111A的时钟可以分为来自外部的时钟和来自内部的时钟。本系统采用的是外部时钟输入,在XTAL引脚和XTALI引脚间接入了一个频率为24.576MHz的是石英晶体振荡器,用于产生系统所需要的工作时钟。再由外部时钟驱动产生行锁定时钟LLC (27MHz ), LLC2 (13.5MHz)和时钟参考信号CREF (13.5MHz,相对LLC2有一定的延时)。时钟的产生还受到片选信号CE的影响,只有当CE为高电平才有效,低电平时SAA7111A被复位,该引脚不产生周期信号。另外,为了使系统工作稳定,将数字地与模拟地分开,中间用电感连接。为了降低电源的纹波干扰,在每个电源引脚的输入端都加了100pF的滤波电容,并将模拟电源和数字电源分别供电。

解码接口控制及数据存储

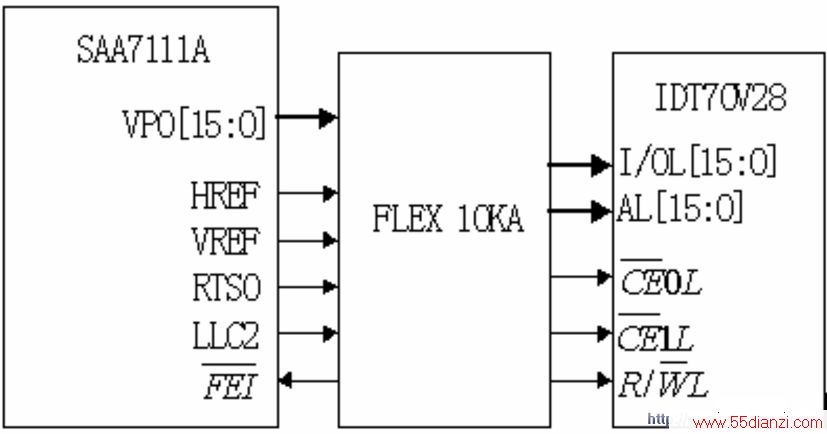

SAA7111A解码输出的数据必须在FPGA的控制下按照指定的方式存储到双口RAM中,其基本的接口电路如图5所示。

图5

其中FLEX 10KA为Alera公司的FPGA,IDT10V28为双口RAM, SAA7111A开始工作后,将输出的场同步信号VREF、行同步信号HREF、奇偶场信号RTS0、像素时钟信号LLC2均送往FPGA,FPGA根据这些信号产生数据存储所需要的片选信号和、读/写控制信号以及存储地址,将采集得到图像数据存储到双口RAM中指定的存储单元,供DSP处理。

SAA7111A的工作方式的配置

SAA7111A工作方式的设置要通过其内置的I2C总线实现。SAA7111A是基于PC机作为平台的EVIP,其所有的可编程功能是通过I2C总线对内部的32个寄存器相位的控制位置设置相应数值来完成的。DSP除了双向的数据口外,没有通用的双向I/O、,不能直接与I2C总线接口。但DSP有两个多通道缓冲串行接口MCBSP, 每个MCBSP的接口信号包括:接收数据DR、发送数据DX、发送时钟CLKX,接收时钟CLKR、接收帧同步FSR、发送帧同步FSX和外部输入时钟CLKS。其中发送时钟CLKX,接收时钟CLKR、接收帧同步FSR、发送帧同步FSX为双向引脚,因此可以通过设置控制寄存器SPCR1、SPCR2和MCBSP引脚控制寄存器PCR的相应位,把它们配置成通用IO口,通过MCBSP(多通道缓存串口)来模拟I2C总线,对SAA7111A进行配置。

结语

SAA7111A将模数转换、自动钳位、自动增益控制、时钟产生、多制式解码等许多复杂的功能集成到一块芯片之内,使得结构简单,便于调试,可靠性也得到了极大提高,从而为 实时图像 采集系统提供了极大的方便。随着计算机和多媒体处理技术的不断提高,其在视频图像采集系统中的作用将越来越大。

本文关键字:暂无联系方式元器件特点及应用,元器件介绍 - 元器件特点及应用

上一篇:小尺寸单片机在便携式设备中的应用