1����

����ADSP2116x�Ǹ����ܵ�32 b���㴦��������һ��������оƬ�ϼ����˾���ǿ�������������������ںˡ���ȴ�SRAM��������ʽ���ⲿ�ӿںͶ�����I/O��������������һ��������ϵͳ����������ṹ��SHARC����CPU����ָ��cacheʹ��ADSP2116x��ָ���Ϊ������ָ�6���������߷ֱ����ڳ���洢����PM�������ݴ洢�� (DM), ����ͬʱ��PM��DM�������ݷ��ʡ��߱����Ż��ģģͣ����жϵĴ������, ʹ�����ⲿ�����ݽ��������������ڴ������ں˵�������̡�

�������⣬Ƭ�ڵ������ӿں������ٲ�������ʹ��Ƭ�Ĵ����������κ� ������Դ���ɹ��ɶദ�������С���Щ�ص�ʹ�ø�ϵ�е�оƬ�㷺Ӧ�����״��źŴ���������ͨ��ϵͳ����ҽ���豸�����ij��ϡ��ж���DSP���ⲿ�豸������Ϣ����������Ҫ�ķ�ʽ֮һ������жϴ������ִ�ʵʱ�źŴ�������Ҳռ�о������صĵ�λ��������Ҫ������ ADSP2116x���жϻ��ƣ������������жϴ�����ʵ�ʹ��̵�Ӧ�á�

2ADSP2116x���жϻ���

����ADSP2116xϵ��оƬ�ṩ��32���ж�Դ��������4����ϵͳ�����ģ���4�����û������ж� �������24����ΪϵͳԤ�ȶ���õ��жϡ�

�������Ƿ�Ϊ3�����ȼ������е�2���������ε��жϾ�����ߵ����ȼ�����������22���������ж���Ϊ�͵����ȼ���ͨ������Ӧ��״̬�Ĵ��������ã��û�������ѡ��ؽ��ж�Դӳ�䵽��22���������жϡ�ͨ����ѯ��Ӧ�ļĴ���״̬���û����Բ�ѯ�ж��Ƿ������жϷ��ص�ַ��״̬��Ϣ��оƬΪÿ���ж�Դ������һ��Ωһ���жϺţ����ж��������У�ÿ���ж϶���Ӧ��4���жϷ���ָ�

2.1�ж�Դ

����ADSP2116xϵ��оƬ�ṩ�˷ḻ���ж�Դ����Ҫ������

����(1)�������ж�

��������жϾ�����ߵ����ȼ�����ϵͳ��λ����������ͨ������EMU��������ʱ �жϷ��������Dz��������жϡ�

����(2)ϵͳ��λ�ж�

��������жϾ��еڶ��ߵ����ȼ���������ͨ������RESET��������ʱ�жϷ�������Ҳ�Dz��������жϡ�

����(3)�����ж�

�������ⲿ�豸ͨ������IRQ0~IRQ2��������ʱ�жϷ����������ǿ������жϡ�

����(4)�ദ���������ж�

�������ദ����ϵͳ�е�ij��DSPдVIRPT�Ĵ���ʱ�жϷ��������ǿ������жϡ�

����(5)Ƭ�����õ������ж�

�����紮�п��жϡ���·���жϡ�DMAͨ���жϡ���ʱ���жϵȣ����Ƕ��ǿ������жϡ�

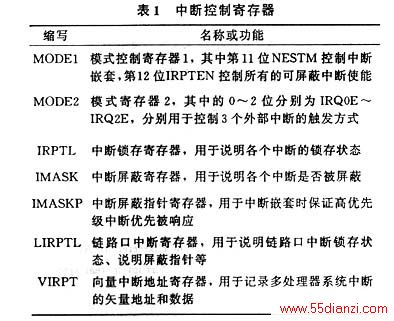

2.2�жϿ��ƼĴ���

����ADSP2116x���ø���״̬�Ĵ���������ж����桢�ж����εȹ����������˵�����жϿ����йصļĴ������1��ʾ��

��

2.3�жϵĴ���

����ADSP2116x֧��2���жϴ�����ʽ����Ե�����͵�ƽ�������û�����ͨ�����üĴ���MODE2 �е�IRQ0E~IRQ2E��ѡ����������жϵĴ�����ʽ���ڵ�ƽ�����Ĺ�����ʽ�£���ʱ���ź�C LKIN�����������DSP�������źŵĵ�ƽΪ��ʱ�����жϷ������ڴ��������жϷ������֮ǰ�����źŵ�ƽӦ��Ϊ�ߣ�����DSP����Ϊ�ַ�������һ���жϡ��ڱ�Ե�����Ĺ�����ʽ�£���CLKIN����������������ź�Ϊ�ߵ�ƽ��������һ����Ϊ�͵�ƽʱ�����жϷ�����

�����Ƚ϶��ԣ���Ե�������ⲿӲ����Ҫ����ͣ���Ϊ���ж�֮�ط�ת��ƽ����ƽ���� ���ŵ������ڵ�����ʱ����ж��豸�ܹ�����һ����ƽ�����ߣ��������ϵͳ����չ��

2.4�жϵ�����

��������һ���ж�֮��DSPͨ�������ж�����Ĵ���IRPTL��LIRPTL�е���Ӧλ����¼�� ���������жϡ��жϷ���֮�����������жϷ������ʱDSPÿ�����ڶ�Ҫ������2 ���Ĵ����е���Ӧλ�������㣬�Ա�֤��ִ���жϷ�������ʱ��ͬһ���жϲ��ᱻ���档 ֱ���жϽ�����DSP�Ž���������λ�����㡣ʵ���ϣ�����RESET��EMU�жϣ�������ж϶��ǿ����εģ�Ҳ����������Ӧ���жϣ����Dz�ִ���жϷ������ �����һ�������ε��жϱ�����֮��DSPҪ�ȵ�����жϿ���֮�����ִ����Ӧ�ķ������

2.5�жϵ�Ƕ��

����ADSP2116x֧���жϵ�Ƕ�ס��ڲ������ж�Ƕ��ʱ�������ȼ����жϲ����жϵ����ȼ��жϵķ�����������ȼ����жϷ���֮��DSP�����ж����棬ֱ����ǰ���жϷ������ִ�����֮��ſ�ʼִ���Ѿ�������жϡ��������ж�Ƕ������£������ȼ����жϾͿ�����ʱ�жϵ����ȼ��жϵķ������ʱ��DSP��������ȼ��жϣ�ֱ��Ƕ����֮��ż���ִ�е����ȼ����жϷ������

�����ж�Ƕ����֮��DSP�����ж�����ָ��Ĵ���IMASKP����һ����ʱ���ж����Σ����������αȵ�ǰ���ȼ����ߵ��жϣ�������������������ͬ���ͼ�����͵��жϡ�Ҳ����˵��ֻ��Ӧ�������ȼ����жϣ�����Ҫ�ȵ�ǰ���жϷ������ִ�����֮�����Ӧ��ͬʱ����ʱ���ж����β���Ӱ���ж����μĴ���IMASK��ֵ��

�������ж�Ƕ������£���������ȼ��жϷ���֮�������ַ����˸������ȼ����жϣ���ʱ�����ȼ��жϵķ������Ҫ�ӳ�һ�����ڲſ�ʼִ�С�����ӳ�����ִ�б��жϵĵ����ȼ��жϷ������ĵ�һ��ָ��������ڸ����ȼ��жϷ������֮�������ȷ�ؼ���ִ�е����ȼ��жϵķ������

2.6�ദ�����ж�

����ADSP2116xϵ��оƬ�IJ��й���������ǿ���������жϻ����У�������֧�ֶദ�����������жϣ�����жϿ����ڶദ����ϵͳ�и���DSP֮����ͨ�ź�ͬ�������ⲿ������������������������DSP�������жϼĴ���VIRPT��д��һ���µĵ�ַʱ���жϷ�������Ӧ�ദ�����ж�ʱ��DSP�Զ���״̬��־ѹջ�����ҿ�ʼִ��VIRPT�Ĵ�����ָ����ַ���жϷ�������жϷ���֮��DSP���Զ��ָ�״̬��־��DSPͨ������ϵͳ״̬�Ĵ���SYSTA�е�VIPD λ����¼�ദ�����жϵķ������ദ����֮��ͨ�ŵij��������ʱ���VIPDλ��ȷ��DSP�Ƿ��ܽ���һ���µ�VIRPT��ַ��Ҫע����ǣ�DSP���ܶԱ�����VIRPT�Ĵ������в�����

3Ӧ�þ���

������DSPΪ���ĵ�ʵʱ�źŴ���ϵͳ����Ҫ���ϵغ��ⲿ�豸�������ݺ�״̬��ͨ�ţ��ڻ���ADSP2116x��DSPϵͳ�Ŀ��������У���õ����жϰ����ⲿ�豸�жϺ�DMAͨ���жϡ�����ֱ���ϸ�������������͵��жϲ���������ij�����롣

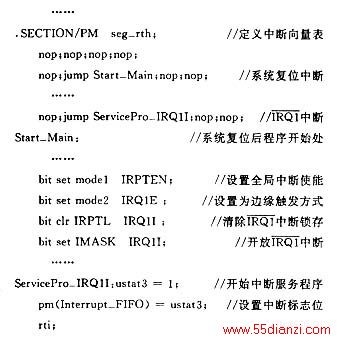

3.1�����жϵ�Ӧ��ʵ��

����ADSP2116x�ṩ��3�������жϣ�������ͨ������IRQ0~IRQ2�����룬����IRQ2���жϼ�����ߣ���IRQ0���жϼ�����͡��ٶ�DSP ��������������Ǵ�ǰ�˵�FIFO�õ������FIFO�������������Ҫ������жϵķ�ʽ֪ͨDSP����Ӧ���ж�Դ��IRQ1����ô����ij�����������һ���ܣ�

����

���������κ��жϴ�����˵���ȶ�Ҫ�����ж���������ÿ���ж�Դ����Ωһ���жϺţ�ÿ���ж� �Ŷ�Ӧ��4���������ָ���4��ָ����ȫ���û����塣ÿ���жϺŵ�������ַҲԤ����оƬ���塣������ADSP21161�У���λ�жϵ��жϺ�Ϊ2���ж�������ַΪ0x40004��IRQ1�жϵ��жϺ�Ϊ7���ж�������ַΪ0x4001C�������жϵ��жϺź��ж�������ַ���Բο����ף�1,2�ݡ��Ĵ���MODE1�е�IRPTENλ���ڿ������еĿ������ж�ʹ�ܣ������ λΪ0����оƬ����Ӧ�κεĿ������жϡ�

������FIFO���Ƶ�·�ж�FIFO�������Ѿ�����Ҫ��֮��IRQ1�����ƽ�ɸ߱�Ϊ�ͣ���ʱIRQ1�жϷ����������������Ĵ�����DSP����ͨ�����жϷ�����������ñ�־λ�Ȱ취����ѯFIFO�������Ƿ�����Ҫ�����������жϵķ�ʽ�������FIFO��DS P���湤��״̬��ͨ�Ź��̡�

3.2DMAͨ���жϵ�Ӧ��ʵ��

����ͬ��������������У��ٶ���DSP��FIFO�е������Ѿ�����Ҫ��֮��Ϊ�˳������DSP���ݴ��ͺ����ݴ����IJ����ԣ�DSP����DMA�ķ�ʽ��FIFO�ж�ȡ���ݡ��ٶ���Ҫ��������ݸ���Ϊ32�����õ�DMAͨ��Ϊͨ��10��DMA�������֮��ͬ��Ҫ���жϵķ�ʽ֪ͨDSP�� ��ô����ij����ܹ������һ���ܡ�����DMA���õ���ϸ���̿��Բο����ף�3�ݡ�

���Ĺؼ��֣�������ϵ��ʽ�ۺ�-��������Ƭ��-�����豸 - �ۺ�-����