随着计算机技术、微电子技术、网络技术和自动控制系统的发展,基于多种微处理器的计算机控制系统已大规模应用于工业控制领域。这种体系结构一般都由上位机系统和下位机系统组成,上位机系统可以充分利用丰富的软件资源、强大的系统和网络功能,进行人机交互操作、数据分析、数据处理、数据存储以及网络的连接,以形成工业控制系统的局域网络;下位机系统则使用控制功能强、抗电磁干扰好、易于开发、具有智能的控制系统如单片机系统、PLC等,主要用于数据采集、数据转换等一些具有特殊要求的工业控制过程。上位、下位机系统采用传统的RS-485或其它总线方式连接,如图1所示。

这种系统结构方式主要存在抗电磁干扰性能较差、网络及数据传输慢和硬件资源浪费等问题,整个系统还存在高性能CPU、存储器与低性能传输系统之间的矛盾,不适合用于高速数据采集系统中。

随着技术的发展以及控制对象生产工艺的要求,工业控制系统具有更高的实时性,对数据的采集和传输有了更高的要求,因此以上述方式组成的控制系统的缺点越来越突出。为了解决上述问题,作者将下位机系统作为上位机系统的功能扩充板,以减少上位机系统与下位机数据传输的距离,提高数据传输速率以及准确性,减少电磁干扰。

下位机系统由CPU、RAM、ROM、数据缓冲器、数据锁存器、A/D(或D/A)转换电路等单元组成,使用上位机系统的电源、数据线、地址线和信号控制线,减少了数据经网络传输过程,避免了由于传输线路受电磁干扰而带来的一系列问题。数据存储体系采用上位、下位机系统都可以访问的高速存储器解决了由于传输问题而导致的瓶颈,充分发挥高速存储体性能,提高了数据传输的速度。上位机系统使用TCP/IP通讯协议,连接多个上位机系统构成控制系统网络。

1 工作原理

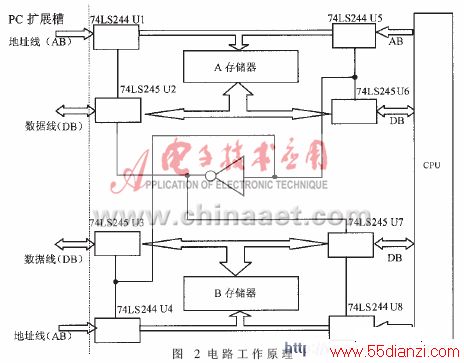

以上位机系统的工业IPC机和下位机系统的HD64180为例介绍系统的工作原理。电路原理图如图2所示。

下位机系统由CPU、数据存储器、数据缓冲器、数据锁存器以及译码电路等组成。可作为上位机的一个外部设备,使用地址可在I/O保留区C0H之后,目的是避免与上位机其它外部设备的地址产生冲突[1]。由于存储体使用了上位机系统的部分数据线、地址线和控制信号线,可能产生上位、下位机系统同时对高速存储体访问的冲突,为了解决此问题,在下位机系统中使用两组高速存储体A、B。存储体的地址在下位机系统中可安排在ROM的地址之后,在上位机系统中则在A000H之后,目的是避免与上位机系统内部存储器地址产生冲突。数据缓冲与锁存采用单、双向总线收发器将上位、下位机系统的数据线、地址线和控制信号线对存储体的操作隔离,通过对总线收发器使能端的控制决定CPU对存储体的访问。因此,对存储体的读、写控制权在任一时刻只能属于两个CPU之一。