摘要:将扩频技术和嵌入式技术结合起来,设计了一种数字扩频收发信机,它是双通道的,每一个通道都包括硬件和软件两部分。硬件部分由语音编解码电路、嵌入式微处理器、电平转换电路、语音数据扩频解扩调制解调电路、锁存及控制信号产生电路、外部存储器和射频单元电路组成;软件部分由系统启动加载程序和收发机系统的主程序两部分组成。通过软件编程、调试、下载,硬件焊接连线,通电调试,发送通道实现了话音录入、扩频和BPSK调制、无线发送;接收通道实现了无线接收,BPSK解调、解扩和播放;两通道可同时进行;在无线传输时,最远传输距离可达1 km左右,表明达到了设计要求。

关键词:嵌入式系统;扩频;发射:接收

O 引 言

嵌入式系统就:是一个具有特定功能或用途的计算机软硬件结合体,或指装入另一个设备并且控制该设备的专用计算机系统 嵌入式系统的最大特点是其具有目的性和针对性,即每一套嵌入式系统的开发都有其特殊的应用场合与特定功能。嵌人式系统包含硬件和软件两部分。硬件架构以嵌入式处理器为中心,配置存储器、I/O设备、通信模块等;软件部分以软件开发平台为核心,向上提供应用编程接口API,向下屏蔽具体硬件特性的板级支持包BSP。嵌入式系统中,软件和硬件紧密配合,协调工作,共同完成系统预定的功能。

扩频通信是当今国际上高新技术热点之一,其理论基础是香农(C.E.Shannon)的信道容量公式。该公式表明,在高斯信道中,当传输系统的信号噪声功率比SNR下降时,可用增加系统传输带宽W的办法来保持信道容量C不变;对于任意给定的信号噪声功率比,可以用增大传输带宽来获得较低的信息差错率。扩频技术正是利用这一原理,用高速率扩频码来达到扩展待传输数字信息带宽的目的。扩频通信系统的带宽比常规通信体制大几百倍至几千倍,故在相同信噪比的条件下,具有较强的抗噪声干扰能力。

1 基于嵌入式系统的数字扩频收发信机的硬件设计

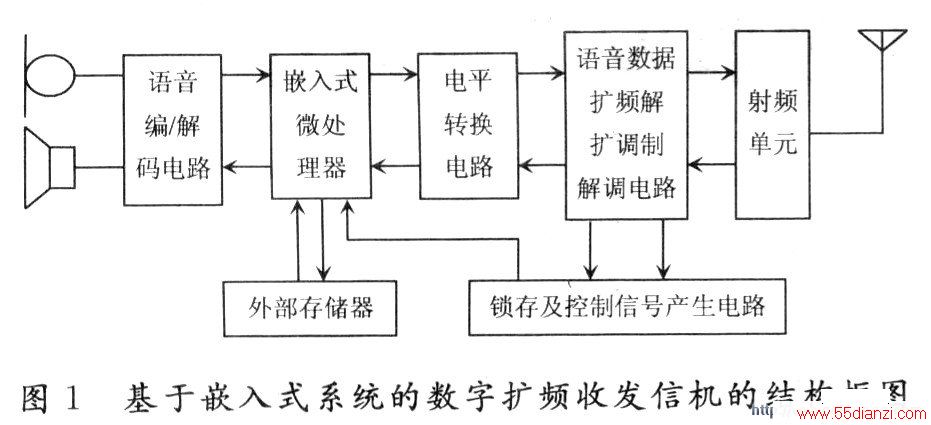

设计的基于嵌入式系统的数字扩频收发信机结构框图如图1所示。

该数字扩频收发信机是双通道的(图中只画出单一通道)。通道由语音编解码电路、嵌入式微处理器、电平转换电路、语音数据扩频解扩调制解调电路、锁存及控制信号产生电路、外部存储器和射频单元电路组成。

语音编解码电路采用PHLIPS半导体公司生产的低功耗立体声音频编解码芯片UDAl344TS。该芯片3.O V电源供电,可工作在L3微控制器模式,也可工作在静态引脚工作模式,通过模式控制引脚MCl(8脚)、MC2(21脚)设置为静态引脚工作模式(均为高电平),在该模式下,可控制的特征有系统时钟选择、数据输入/输出格式设置、重低音和静音控制以及ADC控制,这些特征是由引脚MPl(9引脚)、MP2(13引脚)、MP3(14引脚)、MP4(15引脚)、MP5(20引脚)控制的。

嵌入式微处理器选用SAMSUNG公司为手持设备设计的低功耗、高集成度基于ARlM920T核的微处理器S3C2410X。该处理器集成了16 KB指令和16 KB数据缓存、MMU、外部存储器控制器、LCD控制器、NAND FLASH控制器、4个DMA通道、3个UART通道、1个I2C总线控制器、1个I2S总线控制器、4个PWM定时器和一个内部定时器、通用I/O口、实时时钟、8通道10位ADC和触摸屏接口、USB主/从接口、SD/MMC卡接口等。

语音数据扩频解扩调制解调电路选用Zilog公司研制的可编程单片直接序列扩频收发芯片Z87200。该芯片包括发送部分、接收部分和控制部分,它将扩频通信收发主要电路的各个部分都集成于一块100个管脚的芯片中。发送部分包括了发送数据的白化处理、串并变换、差分编码、PN码产生、扩频、QPSK/BPSK调制及发定时控制,完成由数据输入到已调中频信号输出的扩频、调制处理。接收部分包括中频到基带的数字下变换、PN码产生、数字匹配滤波、解扩、相关峰检测、差分解调、并串转换、去白化处理、数控振荡器及位定时处理等,完成由数字中频信号输入到数据输出的全过程解调解扩处理。此外,Z87200还设置了86 B的片内寄存器,用于对芯片功能的编程设置,使得对扩频系统的设置具有灵活性,芯片具有通用性,可与计算机或单片微处理器连接,完成对内部寄存器的编程控制。

电平转换电路采用MAXIM公司的双向8通道电平转换芯片MAX3001E。由于嵌入式微处理器S3C2410X工作电压通常是3.3 V,而直序扩频收发器Z87200工作电压通常是5 V,所以可采用多个MAX3001E来连接这两个芯片,以实现它们之间。的逻辑电平转换。

锁存及控制信号产生电路采用74LV373锁存器和复杂可编程逻辑器件EPM7128SLC84-15。在通过接口控制单元向直序扩频收发器Z87200读写数据时,为了确保数据的稳定,采用74LV373锁存器对要读写的数据先进行锁存,然后才完成数据的读写。EPM7128SLC84-15是ALTERA公司生产的一款MAX7000S系列的CPLD器件,用VHDL编程设计一个8位同步移位寄存器和一个9位同步计数器,在.Max +PlusⅡ开发平台上进行编译仿真后下载在CPLD器件EPM7128SLC84-15上。由于直序扩频收发器Z87200被设置为突发工作模式,为方便数据处理,可设置突发块的长度为8符号/帧,配合使用9位计数器和8位移位寄存器,每移位9次可得到真正需要的8位语音数据。

本文关键字:嵌入式 嵌入式系统-技术,单片机-工控设备 - 嵌入式系统-技术