随着物联网概念的提出及相关技术的发展,网络化测量控制已成为测控系统发展的必然趋势。然而,当前国内外工业控制领域普遍使用且技术相当成熟的PLC(Programable LogIC Controller)基本都不支持网络,也不能简单升级具有网络功能,且模式较为单一。因而,设计与实现了一种网络化通用测控系统平台,以实现网络化测控需求且具有一般平台的通用性能。本文主要介绍了ARM嵌入式系统与ZigBee无线技术相结合的通用网络测控平台的硬件设计。

1 系统硬件总体设计

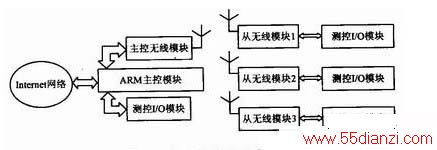

基于ARM的通用网络测控系统硬件架构如图1所示,本系统在测控端采用基于ARM的CPU,通过网络接口与Internet相连,外围扩展有数字量输入/输出模块、模拟量输入/输出模块及无线ZigBee组网数据传输模块。硬件设计的主要研究内容:基于ARM的嵌入式主控硬件平台、ZigBee无线网络数据传输模块、测控I/0模块硬件以及硬件系统的通用性指标和网络化性能的分析测试。

图1 系统硬件架构

2 ARM主控模块硬件

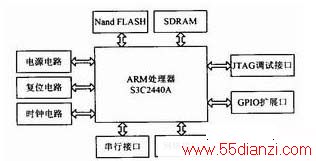

系统核心芯片是Samsung公司生产的基于ARM920T核16/32位RSIC(Reduced Instruction Set Computer,精简指令集计算机)微处理器S3C2440A,该芯片资源丰富、运算速度快、功能强大,且价格相对合理。核心板系统框图如图2所示。

图2 核心板系统框图

2.1 存储器电路

FLASH存储器采用Samsung半导体生产的64M×8 b的K9F1208U0M Nand FLASH存储器芯片。本系统使用了一片该芯片构成64MB的FLASH,系统的启动代码Bootloader文件、内核镜像文件以及文件系统均存于此。SDRAM存储器采用Hynix生产的4 Banks×4M×16 b的HY57V561620 CSD-RAM芯片,为了保证系统的运行速度,本系统采用两片该芯片并联构成32位数据存储器。

2.2 JTAG调试接口

JTAG(Joint Test Action Group,联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。它在芯片内部封装了专门的测试电路TAP(Test ACCess Port,测试访问口),通过专用的JTAG测试工具对内部节点进行测试,同时可用于在线编程。标准的JTAG接口是4线:TMS,TCK,TDI,TDO,分别为模式选择、时钟、数据输入和数据输出线。系统采用20针的标准接口,用于在线调试及系统Bootloader的下载。

2.3 电源与系统时钟电路

电源设计的可靠性关系到系统运行的稳定与否。本系统输入电源为5 V,通过LM1117芯片将其稳压至3.3V,使用大电容抑制低频干扰,小电容抑制高频干扰,用于芯片接口的供电,同时采用专用电源芯片MIC5219BMM,为内核提供低噪的1.3 V电压,以确保系统供电稳定。

系统时钟主要分为主频时钟FCLK,AHB总线设备时钟HCLK,APH总线设备时钟PCLK。本系统采用外部12 MHz晶体振荡器,通过S3C2440的设置模式选择引脚OM[2:3]均为低电平的组合方式来选择S3C2440的时钟源为外部晶振XTIPLL。同时,可通过片内的两个锁相环MPLL和UPLL来得到内核时钟和USB时钟。

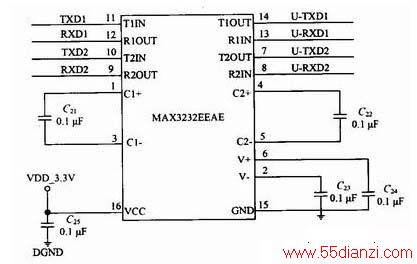

2.4 串行接口电路

当前,基本上各种处理器上都具备串口,本系统中的串口主要用于前期调试以及与主无线模块的通信。由于CPU串口引出脚电平不是标准RS 232电平,因此在与PC机连接调试时需进行电平转换,而与无线模块通信则可直连。可以在Linux内核串口驱动的基础上修改为ZigBee的数据收发驱动,其电路如图3所示。

图3 串行接口电路

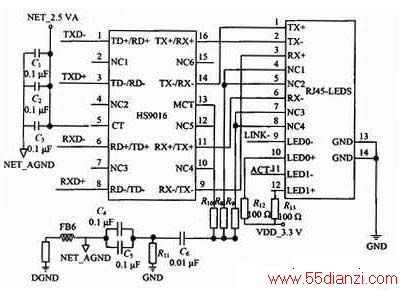

2.5 网络接口电路

网络接口电路是该系统中重要的硬件部分。为了保证网络数据传输的稳定流畅,本系统中采用10/100 Mb/s自适应以太网MAC控制器芯片DM9000A,该芯片具有一个10/100 Mb/s自适应的PHY和4K DWORD值的SRAM,物理协议层接口完全符合IEEE 802.3u规范,支持IEEE802.3x全双工流量控制。主控模块板上nGCS3接DM9000A的片选CS#,地址配置为0x18000002,LDATA[15:0]接DM9000A数据位SD[15:0]构成16位数据总线模式。此外,采用HS9016用于I/O隔离变压,然后连接RJ45接口。隔离电路如图4所示。

图4 网络接口隔离变压电路

3 测控I/O模块硬件

3.1 数字量输入/输出模块

系统实现了8路数字量的输入,8路数字量的输出,采用CH573对数字量输出进行锁存,采用CH245对输入量进行选通。为了节省端口资源,数字量的输入、输出的8根数据线复用,通过控制CH573的锁存信号以及CH245的片选信号来实现输出量和输入量的复用。同时,采用光耦用于端口光电隔离。