内容摘要:5/3小波变换硬件实现常用结构是先完成分裂,再依照分裂后的数据完成预测部分和更新部分的变换,这需要复杂的控制结构。在此采用JPEG2000推荐的5/3小波变换公式,在基于行的列变换基础上提出了一种全新的无数据分裂的结构。该结构放弃地址寻址的数据读取模式,采用读取一维数据流节点的输入方式,从时应的寄存器中读取在多个寄存器中依次流动的数据,省略了数据输入的地址控制模块。由于减少了数据分裂步骤,并且无需控制预测及更新步骤的交替进行,因此简化了小波变换控制系统的结构。在此运用软硬件协同的验证方法,利用计算机软件和FPGA结合,完成图片从计算机端输入,在FPGA中完成小波变换,并输出到计算机显示器上显示的步骤。

关键词:小波变换;软硬件协同验证;FPGA;JPEG 2000

引言

小波分析是当前应用数学和工程学科中一个迅速发展的新领域,而近年来基于小波变换的图像压缩技术以硬件方式推向市场,图片压缩已成为小波变换极其重要的应用领域。而在原有的小波变换的理论基础上发展的基于小波变换的更新算法,不采用Fourier变换作为主要的分析工具,这与经典小波变换相比具有小波构造简单、反变换容易实现、运算速度快和节省存储空间等优点。但其在硬件应用开发上,对中间数据量要求较大,占用较多寄存器,因而通过硬件结构的探索来减小寄存器的开销,成为小波变换图片处理的一个重要分支。

本文提出了无分裂步骤的5/3小波变换结构,完成了该结构的FPGA硬件实现,并结合计算机端Matlab软件,正确完成图片变换验证。

1 硬件结构

1.1 算法实现结构

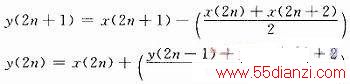

本文采用JPEG2000推荐的5/3小波变换算法,算法公式如下:

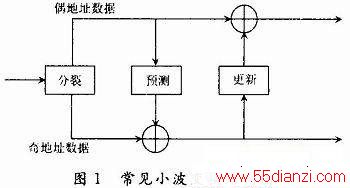

常见的小波变化实现结构如图1所示,先完成分裂,再进行预测,最后完成更新步骤。分裂步骤是指通过对数据地址n的奇偶进行判断,将数据分裂为奇地址部分和偶地址部分。输入奇地址部分数据,进行预测部分运算,并输出细节数据;输入偶地址部分数据,完成更新部分运算,输出平滑数据。因此需要根据输入数据的地址,对数据进行分裂,或控制预测部分和更新部分交替工作。

本文提出一种全新的运算结构,以一维数据流输入数据,无需数据分裂步骤,并且不需要控制预测部分和更新部分的运行和停止,通过对数据流固定节点取值,分别完成预测和更新步骤,并根据数据地址的变换,利用数据选择器从2个端口交替读取数据即能控制预测和更新步骤的运行。

1.2 数据存取结构

本文采用基于行的列变化和流水线结构,完成二维小波变化数据处理。输入数据以一维数据流形式逐一输入,变化模块读取数据流中的数据进行数据计算,产生变化结果。

1.2.1 行变换数据存取结构

行变换模块输入数据读取方式,是用读取寄存器中数据流的方式代替地址寻址的数据读取模式。

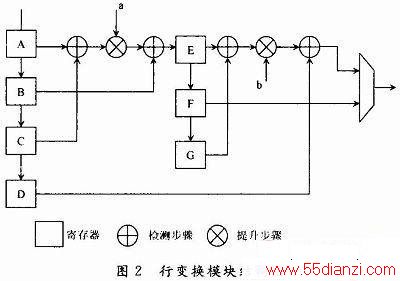

数据依照输入顺序,在寄存器A,B,C,D中依次流动。变换模块在不同的时间分别从A,C和D中读取数据,进行预测和更新的变化步骤。变换后输出的数据存放在列变换模块的寄存器D1和FIFO-A中。行变换模块结构图如图2所示。

1.2.2 列变化数据存取结构

在进行列变换时,需要读取变换数据点临近行的同列数据。而完成该数据点变换后,进行的是同一行下一列的数据点的列变换。因此需要依次读出相邻4行的同列数据,行数不变,列数依次递增。

为了简单的实现该数据读取的顺序,本文使用3个FIFO来保存连续3行的数据:当输入新一行的第1个数据时,3个FIFO释放出第1个数据(即之前3行每1行的第1个数据),刚好组成完成列变换的相邻4行的同列数据。同时,数据的新1行的数据进入FIFO-A,FIFO-A释放出的数据进入FIFO-B,FIFO-B释放出的数据进入FIFO-C。之后,释放出第2列的数据,并重复上述步骤。

因此在完成数据变换的同时,数据在FIFO-A,FIFO-B,FIFO-C中依次流动。完成该行的所有列数据的变换后,FIFO-A中的数据依次寄存在FIFO-B中,FIFO-B的数据寄存在FIFO-C中,而FIFO-A则寄存了新1行的数据。当下1行的数据输入时,又依照上述顺序,开始下1行的列变换。

1.3 变换模块结构

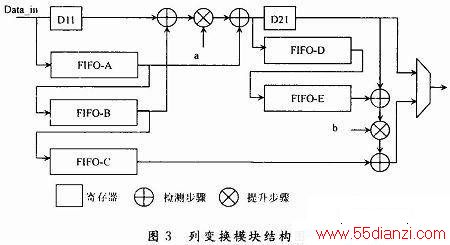

常见的小波变换结构是当输入奇数地址数据时完成预测步骤,当输入偶数地址数据时完成更新步骤。而本文提出的结构不进行数据分裂,直接对数据进行预测和更新,并同时输出到数据选择器。数据选择器对地址奇偶进行判断,选择输出数据,可以得到和常用结构相同的结果。列变换模块结构图如图3所示。

1.3.1 行变换结构

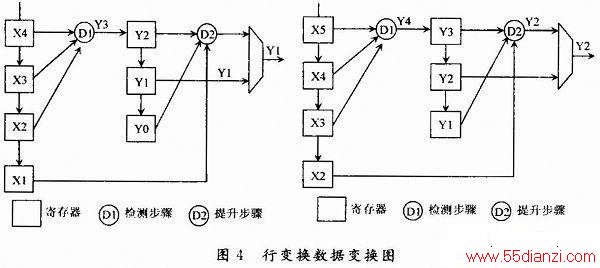

本文提出了无分裂步骤的结构中,行变换时数据流输入后依次寄存在寄存器D1,D2,D3,D4中。如图4(a),寄存器D1,D2,D3,D4中已分别寄存了输入数据X4,X3,X2,X1,而寄存器D5,D6,D7则分别寄存了数据Y2,Y1,Y0。此时利用寄存器D1,D2,D3中的数据X4,X3,X2经过预测步骤,得到预测结果y3=x3-(x2+x4)/2;此前已在寄存器D5,D6,D7中分别寄存了前3个时钟分别完成计算的结果Y2,Y1,Y0,则经过更新步骤可得y1=x1+(y0+y2+2)/4。此时通过数据选择器输出的值Y1是奇数地址,因此仅需要完成预测步骤运算的结果(即寄存器D6中的数据),也就是说输出寄存器D6中的Y1值,放弃更新步骤产生的Y1值。

在下一个时钟沿来临时,X4,X3,X2依次取代X3,X2,X1的位置,输入的X5则寄存在X4的位置,同理Y2,Y1依次取代Y1,Y0的位置,预测产生的Y3值则寄存在Y2,则下一次计算时,寄存器中的值如图4b,预测步骤产生Y4,更新步骤产生Y2,由于是偶数地址,所以通过数据选择器输出经过更新步骤的Y2值。

1.3.2 列变换结构

列变换时,假设第m行的第n列完成行变换后的数据为X(m,n),将该数据寄存在寄存器D1中,下个时钟沿来临时,FIFO-A和FIFO-B中分别释放出第m-1和m-2行的第n列的数据X(m-1,n)和X(m-2,n),同D1中X(m,n)数据共同完成预测步骤生成Y(m,n)并寄存在D2中,同时从D1和FIFO-A,FIFO-B中释放出的数据X(m,n),X(m-1,n)和X(m-2,n)分别寄存进FIFO-A,FIFO-B,FIFO-C。再下一个时钟沿来临时,完成第m行第n+1列的行变换,并寄存在D1中,之后即可按照上述步骤完成第m行第n+1列数据的预测和更新,得出结果Y(m,n+1)。当FIFO把第m行数据完全释放出时,已在该FIFO寄存了第m+1行的完整数据,可以开始下一行的列变换。同理,完成预测步骤的数据寄存在D2,FIFO-D,FIFO-E中,依据预测步骤相似的原理完成更新步骤。之后依据数据的列地址的奇偶,选择不同的Y值输出。

1.4 控制结构

一般的变化模块,均采用状态机的控制方法,利用状态的跳转,来控制行变化和列变化之间的关系,完成预测和更新步骤。

而本文提出了全新的、更为灵活的直角坐标系控制法,即利用行坐标(row-c)和列坐标(col-c)形成一个二维直角坐标系,并将图片映射到直角坐标系上,每一对坐标(row-c,col-c)对应直角坐标系上图片的一个点,也对应该点的变换时刻。通过row-c,col-c的值来判断正在进行变换的行列值,来决定FIFO和变化模块的动作。利用row-c,col-c的末位来判断进行变换的行和列地址分别是奇数地址还是偶数地址,决定是进行预测步骤还是更新步骤。结合计数器,通过输入的图片的行像素值M和列像素值N,分别控制row-c和col-c的跳变。因而可以简单的通过改变M,N值的大小来改变进行变换的图片的大小。

2 结果验证

2.1 采用软硬件协同验证的结构

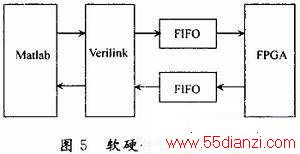

本文采用软硬件协同工作的结构,如图5所示。利用计算机端的Matlab软件从FPGA芯片中读取变换后的RGB数据,并显示在计算机显示器上。

本文关键字:暂无联系方式EDA/PLD技术,单片机-工控设备 - EDA/PLD技术