摘要:按键被广泛用于基于FPGA的数字电路系统设计中,机械式按键开关在按键操作时经常会出现抖动现象,如果不进行消除将会造成电路系统的误操作。基于此介绍了基于VHDL语言的计数器型消抖电路、D触发器型消抖电路、状态机型消抖电路的工作原理、相关程序、波形仿真及结果分析,并下栽到EP2C35F672C8芯片上进行验证,消抖效果良好,性能稳定,可广泛用于FPGA的按键电路中。

关键词:VHDL;消抖;FPGA

0 引言

按键开关是许多电子产品不可缺少的输入设备,在智能化电子产品中,按键开关作为人机交互的主要器件之一,可以实现人机对话,完成各种功能操作,而机械式按键开关由于其低成本、高可靠性被广泛使用。在按键操作时,机械触点的弹性及电压突跳等原因,在触点闭合或开启的瞬间会出现电压抖动,实际应用中如果不进行处理将会造成误触发。常见的硬件消抖方法有:利用电容的充放电原理;利用RS触发的保持功能;由同相器组成的积分去抖电路;用反相器组成的翻转式去抖电路;不可重复触发单稳态等等。本文采用VHDL语言设计了几种按键开关的消抖电路。

1 计数器型消抖电路

1.1 计数器型消抖电路(一)

计数器型消抖电路(一)是设置一个模值为(N+1)的控制计数器,clk在上升沿时,如果按键开关key_in='1',计数器加1,key_in='0' 时,计数器清零。当计数器值为2时,key_out输出才为1,其他值为0时。计数器值为N时处于保持状态。因此按键key_in持续时间大于N个clk时钟周期时,计数器输出一个单脉冲,否则没有脉冲输出。如果按键开关抖动产生的毛刺宽度小于N个时钟周期,因而毛刺作用不可能使计数器有输出,防抖动目的得以实现。clk的时钟周期与N的值可以根据按键抖动时间由设计者自行设定。

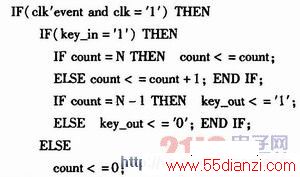

主要程序结构如下:

![]()

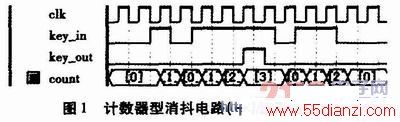

图1是N为3的波形仿真图,当按键持续时间大于3个时钟周期,计数器输出一个单脉冲,其宽度为1个时钟周期,小于3个时钟周期的窄脉冲用作模拟抖动干扰,从图1可以看出,抖动不能干扰正常的单脉冲输出。

该方案的特点是能很好消除按键抖动产生的窄脉冲,还可以滤去干扰、噪音等其他尖峰波,但遇到脉宽大于N个Tclk时钟周期的干扰、噪音等时会有输出从而产生误操作,而对于按键操作要求按键时间必须大于N个Tclk时钟周期,否则按键操作也没有输出。

1.2 计数器型消抖电路(二)

计数器型消抖电路(二)是控制计数器工作一个循环周期(N+1个状态),且仅在计数器为0时输出为“1”。电路设计了连锁控制设施。在计数器处于状态0时,此时若有按键操作,则计数器进入状态1,同时输出单脉冲(其宽度等于时钟周期)。计数器处于其他状态,都没有单脉冲输出。计数器处于状态N时,控制en='0',导致计数器退出状态N,进入状态0。计数器能否保持状态0,取决于人工按键操作,若按键key_ in='1',控制en='1'(计数器能正常工作),key_in='0',计数器状态保持。显见计数器处于状态0,人工不按键,则计数器保持状态0。

www.55dianzi.com

主要程序结构如下:

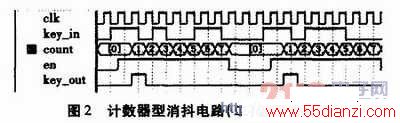

图2是N为7的波形仿真图。在计数器状态为0时,key_in有按键操作,计数器开始连续计数直到计数器状态为0;计数器状态为1-7时,key _in任何操作对计数器工作无影响,计数器在状态为1时,输出一个单脉冲,脉冲宽度为1个时钟周期。

该设计方案的特点是能很好消除按键抖动产生的连续脉冲,对按键时间没有要求,缺点是在计数器状态为0时,遇到干扰、噪音等时会有输出,从而产生误操作。

2 D触发器型消抖电路

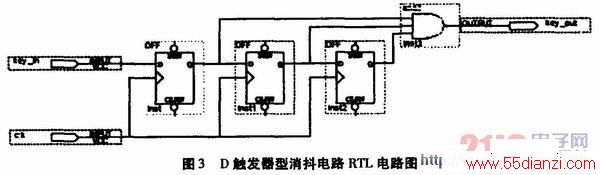

D触发器型消抖电路设计了三个D触发器与一个三输入与门。三个D触发器串行连接,其Q输出端分别与三输入与门的输入端连接,D触发器型消抖电路RTL电路如图3所示。

www.55dianzi.com

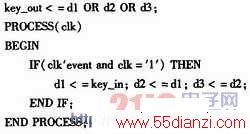

主要程序结构如下:

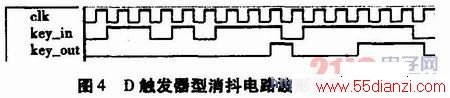

图4为D触发器型消抖电路波形仿真图,由图可见,当按键操作时间大于或等于clk时钟周期的3倍时,输出一个正脉冲,正脉冲的宽度比key_in少2个clk时钟周期。

D触发器型消抖电路与计数器型消抖电路(一)相似,计数器型消抖电路(一)输出脉冲宽度是固定的,D触发器型消抖电路输出脉冲宽度随着按键操作时间长短变化。

3 状态机型消抖电路

状态机型消抖电路采用有限状态机的设计方法来描述与实现,状态机有S0,S1,S2三种状态,在S0状态下key_out输出为低电平,并以clk时钟信号的频率采样按键输入信号,如果key_in=‘0’,则保持在S0状态,并继续采样按键输入信号的状态,如果key_in=‘1’,则转入S1状态;在S1状态下key_out输出仍为低电平,继续采样按键输入信号的状态,如果key_in=‘1’,则转入S2状态,如果key_in=‘0’则转入

S0状态;在S2状态下继续采样按键输入信号的状态,如果key_in=‘1’,则保持在S2状态,key_out输出正脉冲,如果key_in=‘0’,则转入S0状态,key_out输出低电平。

主要程序结构如下:

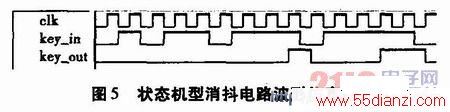

图5为状态机型消抖电路波形仿真图,由图可见,该状态机型消抖电路与D触发器型消抖电路仿真结果一致。

4 结束语

采用VHDL语言实现按键的消抖电路的方法有很多,本文介绍的几种消抖电路都通过仿真分析及实验验证,消抖效果良好,性能稳定,而且各有自己的优势与缺点,设计者可以根据设计需求选择使用。

本文关键字:暂无联系方式EDA/PLD技术,单片机-工控设备 - EDA/PLD技术