char text[] = "I get a EPA PACket,please

give me another,I need you, baby.";

remote_addr.addr = htonl

(0x8080023D);

local_addr.addr = htonl(0x80800233);

conn1 = netconn_new(NETCONN_

UDP);

conn2 = netconn_new(NETCONN_

UDP);

netconn_bind(conn2, &LOCal_addr, 0x88bc);

netconn_connect(conn2,&remote_addr,

0x88BC);

netconn_bind(conn1, &local_addr, 0x88bc);

while((buf1_temp = netconn_recv

(conn1))!=NULL){

//关于netbuf的结构可以参看api.h文件,在该结构体中,成员p是指向pbuf的一个指针

buf1 = netbuf_new();

buf1 = buf1_temp;

payload = buf1->p->payload;

len = buf1->p->len;

netbuf_delete(buf1);

buf2 = netbuf_new();

netbuf_ref(buf2,text,sizeof(text));

netconn_send(conn2,buf2);

netbuf_delete(buf2);

图4 EPA协议栈接收报文处理流程图

3 结语

在完成了整个设计后,只需将控制器接入EPA网络中就能够正常运行了。由于控制器中的处理器使用的是FPGA芯片,有较强的灵活性,能够进行编程、除错、再编程和重复操作,因而可以充分地进行设计开发和验证。当电路有少量改动时候,更凸现出其优势,其现场编程能力可以延长产品在市场上的寿命,可以用来系统升级,从而大大提高了控制器的性能。

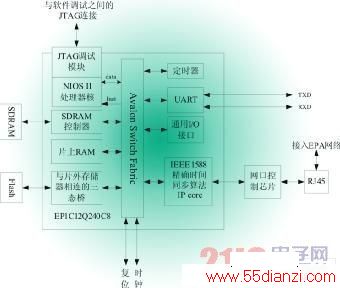

2.2 基于SOPC技术的CPU核心处理模块

整个方案的实现是以接入实时工业以太网络为目的,在芯片内部实现部分EPA协议,同时控制器实现对工业以太网上的其他设备的监控、显示及数据分析。设计中采用ALTEra公司的新一代低成本的FPGA芯片EP1C12Q240C8芯片,该芯片包含有12060LE(逻辑单元),可根据实际需要,配置其NIOSⅡCPU软核、与CPU相连的片内外设和存储器以及与片外存储器和片外设备相连的接口等。

图2是芯片系统结构框图

整个CPU处理器的硬软件设计均在QUARTus II 5.1版本上实现。NIOSⅡ处理器核是Altera公司的第二代用户可配置的通用32位RISC软核微处理器,是Altera公司特有的基于FPGA架构的可配置的软CPU内核,其特性和外设可根据实际需要进行增加或剪裁。所有NIOSⅡ处理器系统使用统一的指令和编程模型,并有三种类型以满足不同设计的要求,分别是快速型、经济型和标准型。在本控制器中,所定制的NIOSⅡ软核选用快速型,该内核处理速度为49DMIPS,耗费的逻辑门数为1400~1800LE,同时带有硬件乘法器和硬件除法器。根据EPA网络对控制器的要求,添加与CPU相连的片内外设和片外设备接口:SDRAM控制器、片内RAM、三态桥、UART、定时器、通用I/O口、LCD显示驱动电路和以太网接口。按照设计要求,在Quartus II 5.1版本下的对CPU的配置情况如图3所示。FPGA芯片可根据实际需要灵活地增加功能,同样对不必要的功能也可进行删减,以满足快速、高效和低成本的设计。