新一代的互联需求持续不断地向软硬件设计施加压力。不断提高的服务质量(QoS),数据信道隔离,数据平滑恢复和完整性等,都是值得考虑的一些指标要求。PCIe就是能够满足上述要求的一种互联技术。

在FPGA中实现一个PCIe接口时,为了确保系统效率,系统抖动,数据时钟开销以及必须满足的端到端总带宽需求,设计师必须考虑数据传输的方式。将一个散/聚DMA(SGDMA)与一个PCIe接口结合起来,通过从本地处理器上卸载一些数据传输负担,以及均摊多通道间的硬件延迟,非常有助于软硬件设计师满足他们的设计需求。本文将讨论采用基于FPGA的SGDMA与PCIe相结合的一些优点。

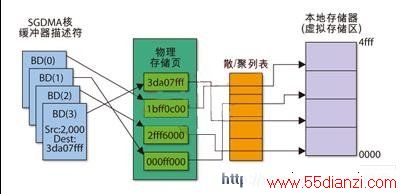

绝大部分的新型DMA控制器都支持散/聚功能,这里,硬件负责数据的转移,驻留在不连续的物理存储器中,不需要主处理器来处理模块间的数据转移。这是通过将DMA缓冲器描述符“链接”到一起来实现的,每个描述符中都含有使SGDMA自动执行数据转移所需的所有信息。当处理支持虚拟存储器的操作系统时,SGDMA得到最普遍的采用。

直接存储器访问实现方案

衡量DMA控制器的收益有以下几种方法:通过定量分析究竟重新获取了多少时钟周期?相关设备驱动的复杂度减少了多少?或者由于“隐藏”数据分发的开销使DMA引擎增加了多少系统总吞吐量?增强型DMA引擎支持的一些功能包括:

* 在线分组缓冲存储

* 本地和前端总线的同时传输

* 延时处理

* 终端事物处理抢断

* 为DMA控制器连接的每条总线提供独立仲裁

当前端和本地总线处于超高负载条件下且传输数据前DMA控制器必须竞用并获取总线占有权时,可以采用在线数据缓冲器。

图1:虚拟存储器环境中的SGDMA控制器。

在FPGA中使用块存储始终是下面几方面的折中,即由于总线占用究竟需要多少临时缓冲器?FPGA中的功能是否需要存储器?使用中间数据存储所导致的附加延迟的代价如何?如果可能的话,在线分组缓冲器可以减少一些系统延迟,即用一条总线去读取数据,而“存储”总线不转送数据。

本文关键字:嵌入式 EDA/PLD技术,单片机-工控设备 - EDA/PLD技术