从工艺选择到设计直至投产,设计人员关注的重点是以尽可能低的功耗获得最佳性能。ALTEra在功耗和性能上的不断创新,那其28nm高端FPGA如何实现功耗和性能的平衡?具体有何优势?

从工艺选择到设计直至投产,设计人员关注的重点是以尽可能低的功耗获得最佳性能。利用Altera在功耗和性能上的不断创新,设计人员能够为他们的最终客户开发独具优势的高性能系统。特别是与其他高端FPGA相比,Altera的28nm高端FPGA功耗降低了15%,而性能却提高了1 个速率等级,更具有功耗优势。

Altera认识到,满足所有需求的方法并不适用于28nm节点。设计人员在其目标应用中需要合适的器件,因此,Altera为其高端FPGA选择了台积电公司(TSMC)的28nm高性能(28HP)工艺,在低成本和中端系列中采用了28nm低功耗(28LP)工艺。

为其Stratix V FPGA选择了28HP工艺之后,Altera做出了几项开发选择以降低器件功耗。本文将介绍从工艺选择到工具以及建模的步骤,保证了在很有竞争力的电源布局下支持实现高性能。设计人员拥有合适的器件和工具,就能够以很低的功耗实现高性能,对设计进行较为精确的早期功耗估算。

功耗和性能考虑

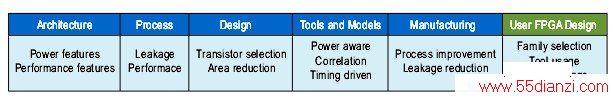

定义28nm高端器件的结构时,需要作出很多决定(参考表1),以尽可能低的功耗实现最佳性能。

表1 功耗和性能考虑

以低功耗实现高性能的结构

在过去几年中,低功耗技术越来越重要,在结构规划阶段就开始考虑降低功耗。Altera以前不断降低功耗的创新是可编程功耗技术及更多地使用了嵌入式硬核知识产权(IP)。在28nm节点,以低功耗实现高性能的新方法包括对于不使用的模块关断SRAM、低电压(0.85 V)结构以及部分重新配置功能等。

使用合适的工艺

工艺选择是Altera 28nm器件系列的关键考虑。如前所述,目标是帮助设计人员针对特定的目标市场和应用来定制功耗。在28nm系列产品上采用两种不同的半导体工艺,与前一代同类产品相比,Altera的28nm FPGA功耗降低了40%。

图1显示了TSMC提供的三种28nm工艺选择。在这些工艺中,大量晶体管具有较大的静态功耗范围。左侧的晶体管静态功耗较低,而右侧的较大。这也体现了静态功耗与这些晶体管性能之间的关系。总体上,晶体管性能越好,静态功耗也就越高。

图1 TSMC 28nm工艺选择

据TSMC资料,28HP工艺是使用高k金属门(HKMG)工艺技术的首选。28HP工艺具有优异的速度和性能,主要面向CPU、GPU、FPGA、PC、网络和消费类电子应用。在同样的漏电/电路门条件下,28HP工艺比40G工艺的速度提高了45%。

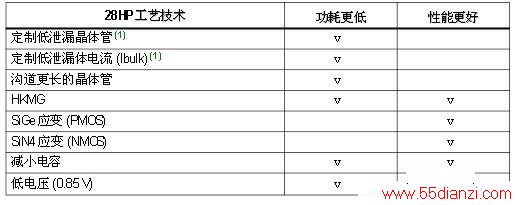

Altera选择TSMC 28HP HKMG工艺,借助与TSMC长达20年的合作关系,优化了Stratix V FPGA低功耗工艺。表2详细介绍了Altera使用高性能工艺降低功耗的步骤。

表2 28HP工艺技术降低了功耗,提高了性能

说明:(1)专门提供仅供Altera 使用的工艺。

大部分TSMC客户必须使用标准工艺,而Altera与TSMC近20年的密切协作使得两家公司能够一起工作开发实现Altera的专用功能。对于28HP工艺,Altera采用可编程功耗技术,联合开发了定制低漏电晶体管和减小了器件体漏电。这两项功能与高性能晶体管相结合,可以调整每一设计模块,以尽可能低的功耗实现最合适的性能。

在28nm时代,Altera继续采用以前Altera获得专利的创新可编程功耗技术,不需要更多的FPGA设计投入,降低了静态功耗。 Altera的QUARTus II开发软件在时间关键通路上应用可选的反向偏压,调整逻辑电压阈值,在需要的地方实现高性能,同时降低了所有其他逻辑的静态功耗。这种可调整能力保证了 Stratix V FPGA设计人员降低了整个设计的静态功耗,同时实现了高性能。

以低功耗实现高性能

FPGA中的每一IP模块都针对功耗和性能进行了设计,目的是以尽可能低的功耗达到特定的性能目的。目标是降低每一工艺代IP模块的功耗。不论是M20K SRAM模块、数字信号处理器(DSP)模块、架构和布线,还是收发器,重点都是以尽可能低的功耗实现合适的性能。

在时序关键通路上使用高性能晶体管,而对于不需要高性能的地方,则使用低漏电晶体管。设计团队在所有不需要高性能的地方使用Altera特有低漏电晶体管或者较长的电路门晶体管。

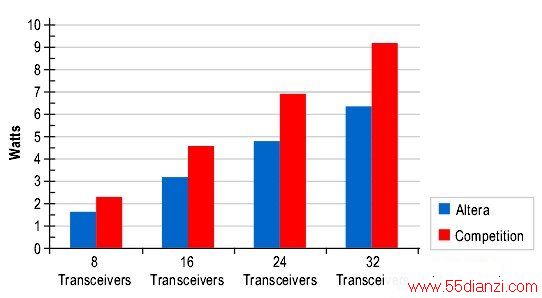

这种灵活性的一个例子是配置能力极强的收发器。不论是运行在6.5G、14.1G还是28G,Altera收发器都具有优异的性能和最低的功耗。在28G时,每通道功耗是200mW。图2对比了几种不同收发器配置时的delta功耗。

图2 收发器功耗对比

实现功耗监控设计流程

从工具的角度看,必须同时考虑功耗和性能。以太高的功耗满足性能要求,或者功耗较低但是没有达到性能目标,这都是不可使用的设计。因此,QUARTus II软件还必须能够在性能和功耗上很好地达到均衡。在没有用户干预的情况下,工具会自动只在需要的地方使用高速块,尽可能降低功耗泄漏以满足性能要求,同时使得所有其他块进入低功耗状态以减小泄漏。此外,还采取了以下降低功耗的措施:

Ÿ 逻辑、RAM 分析、重新规划,以降低动态功耗

Ÿ 群布局减小了走线长度,降低了动态布线功耗

Ÿ 优化布局以减小时钟功耗以及非关键通路信号布线功耗

建模是重要的步骤,因为它保证了功耗模型的正确性,不是最差也不是最乐观。公司可以选择保守、激进或者正确的方式。最终,最适合设计人员的唯一选项是正确地建模。保守选择导致了估算的功耗在市场上看起来并不具有竞争优势。激进的选择导致最终功耗与工具估算的功耗不具有可比性。做到正确的选择尽可能接近硅片实际测量的功耗,同时满足了供应商和客户的要求。

在制造过程中降低功耗,提高性能

提高制造能力,大批量交付器件是提高产量、严格工艺的关键。ALTEra早期以标准功耗指标发售器件,以帮助前沿的客户满足早期原型开发和生产进度要求,然后,严格曲线指标,尽快实现利益,以帮助这些用户满足其产品进度和功效目标。Altera采用这一严格的工艺来交付低静态功耗的新L(低功耗)器件。

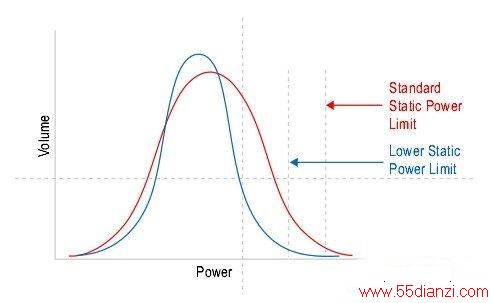

如图3示,减小工艺变化使得静态功耗降低了35%,从而降低了总功耗。由于结温增大和漏电增加是一种指数函数关系,因此,这一方法在较高结温时极大地降低了功耗,满足了当今很多系统设计的要求。

图3 工艺降低了静态功耗

在28HP制造工艺降低功耗的结果非常显著,因此,Altera立即将其应用于独具优势的FPGA上,在产品代码中标以“L”。这种突出显示的订购码旨在将产品立即应用于对功耗敏感的设计中,然后,在所有28 nm产品中继续发挥同样的工艺优势。

在FPGA 设计中使功耗和性能达到均衡

设计人员能够使用高端器件,当这些工具具备了各种低功耗功能以及支持功耗预知的情况下,设计人员自己会确定怎样均衡其每一设计的性能和功耗。他们从选择正确的FPGA系列开始。当需要最佳性能或者最大容量时,选用Stratix V FPGA。在Stratix V系列中,可用的型号包括没有收发器的器件、有收发器的器件,以及重点是DSP应用的器件。

选择好器件后,在FPGA设计过程中,可以使用几种设计方法来降低功耗,包括,逻辑和RAM时钟通道以及部分重新配置等。

即使采用了最佳设计方法、模型和软件,也只有提供了输入后才能进行功耗估算。大部分设计人员熟悉基本动态功耗方程:CV2F X (触发率)。设计工具计算电容(C),已知电压(V)和频率(F)是已知的,但是不知道设计的触发率。确定触发率的最佳方法是运行代表实际系统使用情况的仿真,得到.vcd文件后,使用PowerPlay功耗分析器工具。次优的方法是为I/O建立合适的触发率,根据得到的估算,使用 PowerPlay功耗分析器来产生内部触发率。第三好的方法是使用早期功耗估算器 (EPE),使用以前相似设计的触发率。最不精确的方法是以默认触发率使用EPE。功耗估算的精度与默认触发率和设计实际触发率之间的差值相关。 Altera建议使用 PowerPlay功耗分析器,通过矢量获得最佳功耗估算。