内容摘要:针对机载信息采集系统可靠性、数据管理高效性以及硬件成本的需求,介绍了基于硬件描述语言Verilog HDL设计的SDX总线与Wishbo ne总线接口转化的设计与实现,并通过Modelsim进行功能仿真,在QUARTusⅡ软件平台上综合,最终在ALTEra公司的CycloneⅢ系列FPGA上调试。实验证明了设计的可行性。

关键词 Ver4log HDL;SDX总线;Wishbone总线;Modelsim;QuanusⅡ

随着微电子设计技术与工艺的迅速发展,数字集成电路逐步发展到专用集成电路(ASIC),其中超大规模、高速、低功耗的新型FPGA的出现,降低了产品的成本,提高了系统的可靠性。同时,各种电子产品的复杂度和现代化程度的要求也逐步提高,文中针对机载信息采集系统的可靠性、数据管理的高效性以及硬件成本的需求。设计实现了与Wishbone总线SDX总线的接口转化,完成了数据采集功能模块与SDX总线协议之间的数据传输。

该设计主要采用硬件描述语言Verilog HDL在可编程逻辑器件FPGA上实现,由于数据采集功能模块繁多,而Wishbone总线可以与任何类型的ROM或RAM相连,因此需在SDX总线与数据采集模块中嵌入Wishbone总线,使得整体设计简单、灵活,且数据能够高效、快速的传输。

1 SDX总线协议

1.1 SDX总线结构

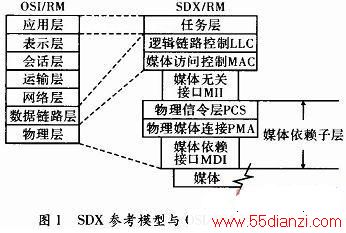

SDX总线属于非平衡配置的点对点和多点链路,站点类型分为主站和从站,其数据传输方式为非平衡配置的指令/响应方式。与国际标准化组织ISO制定的开放系统互联模型OSI/RM相比,参考模型只分为3层:物理层、数据链路层和应用层,如图1所示。

1.2 字格式及其各位场的含义

SDX总线采用面向消息的传输控制规程作为通信协议,选用曼彻斯特Ⅱ双相电平编码,总线最大传输速率20 Mbit·s-1,字长为20位。总线传输速率20 Mbit·s-1时,每字占1μs。规定每次传输一个消息的过程应包括指令字、数据字和状态字几个部分。每种字的字长为20位,有效信息位为16位,每个字的前3位为单字的同步字头,而最后一位是奇偶校验位。同步字头的作用是标识每个字的开始,起字同步作用。奇偶校验采用奇校验,在发送端对16位有效位补齐,而在接收端进行奇校,用于检验字传输中有无错误。需要指明的是:无论是何种字类型,各场的数据总是高位(MSB)传输在先。

(1)指令字结构。

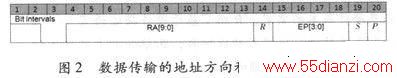

指令字只能由主站发送,它的内容指明主站要与哪个从站对话,规定了该次数据传输的地址方向和服务类型。其格式如图2所示。

方向和服务类型

1~3位:同步字头(SYN),前1.5位为101,后1.5位为000时标识指令字或状态字。

4~13位:10 bit远程模块地址(RA[9:0]),全“0”时为广播地址,其余为各远程模块地址。

14位:读写控制位R。该位为“1”时,表明主站要从被寻址的从站中读取数据;为“0”时,表明主站要从被寻址的从站中写入数据。

15~18位:当RA[9:0]为非全“0”时,EP[3:0]有效。需要强调的是:当RA[9:0]为非全“0”,端点地址为全“0”时,该地址为从站的系统管理访问地址。

19位:状态字指示位S,当该位为“0”时,表明有效字为指令字;当该位为“1”时,表明有效字为状态字。

20位:奇偶校验位(P),该字的奇偶校验位,奇校验有效。

(2)数据字结构。

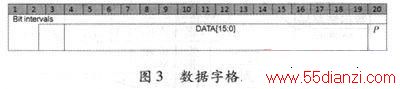

数据字既可以由主站传送到从站,也可以由从站传送到主站。数据字的格式如图3所示。

1~3位:前1.5位为101,后1.5位为111时标识数据字。

4~19位:16 bit长数据(DATA[15:0]),高位(MSB)传输在先。

20位:奇偶校验位(P),该字的奇偶校验位,奇校验有效。

(3)状态字结构。

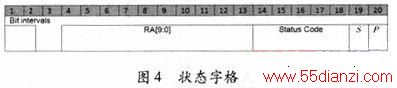

状态字只能由从站发出,是对主站发出的有效命令的应证性信号,是通信中进行差错控制和流量控制的重要手段。状态字格式如图4所示。

1~3位:同步字头(SYN),前1.5位为101,后1.5位为000时标识指令字或状态字。

4~13位:10 bit从站的地址(RA[9:0])。

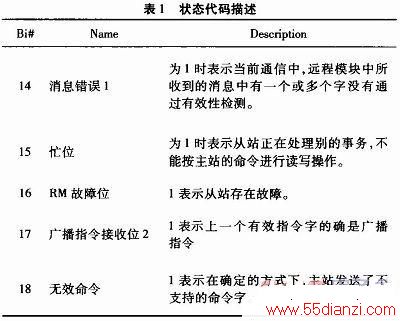

14~18位:状态代码,表示响应模块的通信状态。

19位:状态字识别位(S),当有效字为状态字时,该位为“1”。

20位:奇偶校验位(P),该字的奇偶校验位,奇校验有效。

注释1,只有满足下列判据才认为传输中不存在错误:(1)“字有效”,这是指都以有效的同步字头开始,并且除去同步字头之外其余的都是有效的双相码,有效信息是16位,奇偶校验位一位,且奇校验。(2)“消息有效”,这是指在一次传输中,如果存在一个数据块,那么在指令字与数据字之间,在数据字与数据字之间,消息是连续的,不存在任何“断裂”的情况。(3)“指令有效”,这是指在指令字和数据字各场中不存在非法数据,同时发出的数据块长度应与设置长度相等。如果以上3个判据中有任何一个得不到满足,则消息错误位置位。

注释2,由于广播消息格式要求禁止从站发回状态字,为了解上一个广播指令是否已被从站有效接收,可使用专门的命令类型让某个从站发回状态字,如此位置成“1”,而且忙位置成“0”,即说明上一个指令的确是广播指令,已被该从站有效接收。

2 Wishbone总线协议

Wishbone总线是一种内部总线协议。它可以将片内的各部分以及IP核等连接在一起,用来标准化各个独立部分的接口,以更加方便地架构SOC(Syctem-on-Chip)系统。其特点是结构简单、灵活,只需要少量的逻辑门即可实现,同时完全免费、公开。

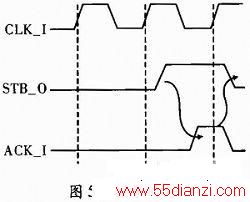

Wishbone总线规范中,使用Master/Slave结构实现灵活的系统设计,Master/Slave有4种互连方式,分别为点对点、数据流、共享总线和交叉互连。且Master和Slave之间使用握手协议,当准备好数据传输时,Master使STB_O有效,且一直保持到Slave的响应信号ACK_O,ERR_O,或RTY_O之一有效。Master在每个时钟的上升沿对响应信号采样,若该信号有效,则置低STB_O,如图5所示。

2.1 Wishbone总线基本传输周期

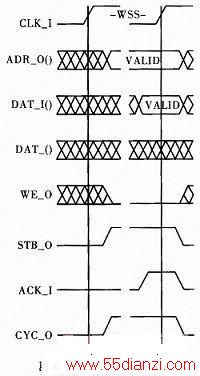

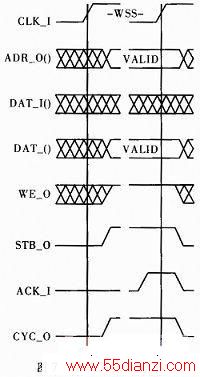

Wishbone总线支持完整的普通数据传输协议,包括单个读写周期、块读写周期等。数据总线宽度为8~64位,地址总线宽度最高可达64位。Wishbone数据总线和地址总线分离,在传输上,保持一个地址、一个数据的传输结构。以下为Wishbone总线单次读、写时序图。图6为单次读周期时序,图7为单次写周期时序。

3 系统设计与实现

系统所有控制逻辑均在ALTEra的CycloneⅢ系列FPGA(EP3C40F)上实现。FPGA的信号线只有系统时钟、串行输入数据,由于SDX总线中传输数据为曼彻斯特码型,因此需将曼彻斯特码解码为BCD码同时将串行输入数据转化为并行数据,将转化后标准的16位并行BCD码输入SDX模块对SDX协议响应,将需要数据读、写的消息响应同时产生数据读、写以及地址信号并发起Wishbone总线操作,实现在Wishbone总线上高效的数据传输。Wishbone总线主要使用点对点的互联方式,将Wishbone总线中Master模块中的输出信号直接连接到Slave模块,其优点是多个数据可以并行处理,从而提高系统的整体数据处理能力。系统的整体设计框图如图8所示。

本文关键字:接口 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术