0 引 言

利用现场可编程逻辑器件产生VGA时序信号和彩条图像信号,并将其作为信号源,应用于电视机或计算机等彩色显示器的电路开发,方便彩色显示器驱动控制电路的调试。计算机显示器的显示有许多标准,常见的有VGA,SVGA等。在这里尝试用FPGA实现 VGA图像显示控制器,这一过程通过编程实现,之后通过软件的测试和仿真,当软件验证无误后完成硬件的下载验证,最终在CRT显示器上实现输出,基本原理就是利用FPGA的可编程原理和VGA的时序控制原理,这在产品开发设计中有许多实际应用。

1 VGA显示原理

VGA(Video GraphICs Array)作为一种标准的显示接口得到了广泛的应用。VGA在任何时刻都必须工作在某一显示模式下,其显示模式分为字符显示模式和图形显示模式,而在应用中讨论的都是图形显示模式。

VGA的图形模式分为三类:CGA,EGA兼容的图形模式;标准VGA图形模式;VGA扩展图形模式,后两种图形模式统称为VGA图形模式。文中基于标准VGA模式来实现。工业标准的VGA显示模式为:640×480×16×60。

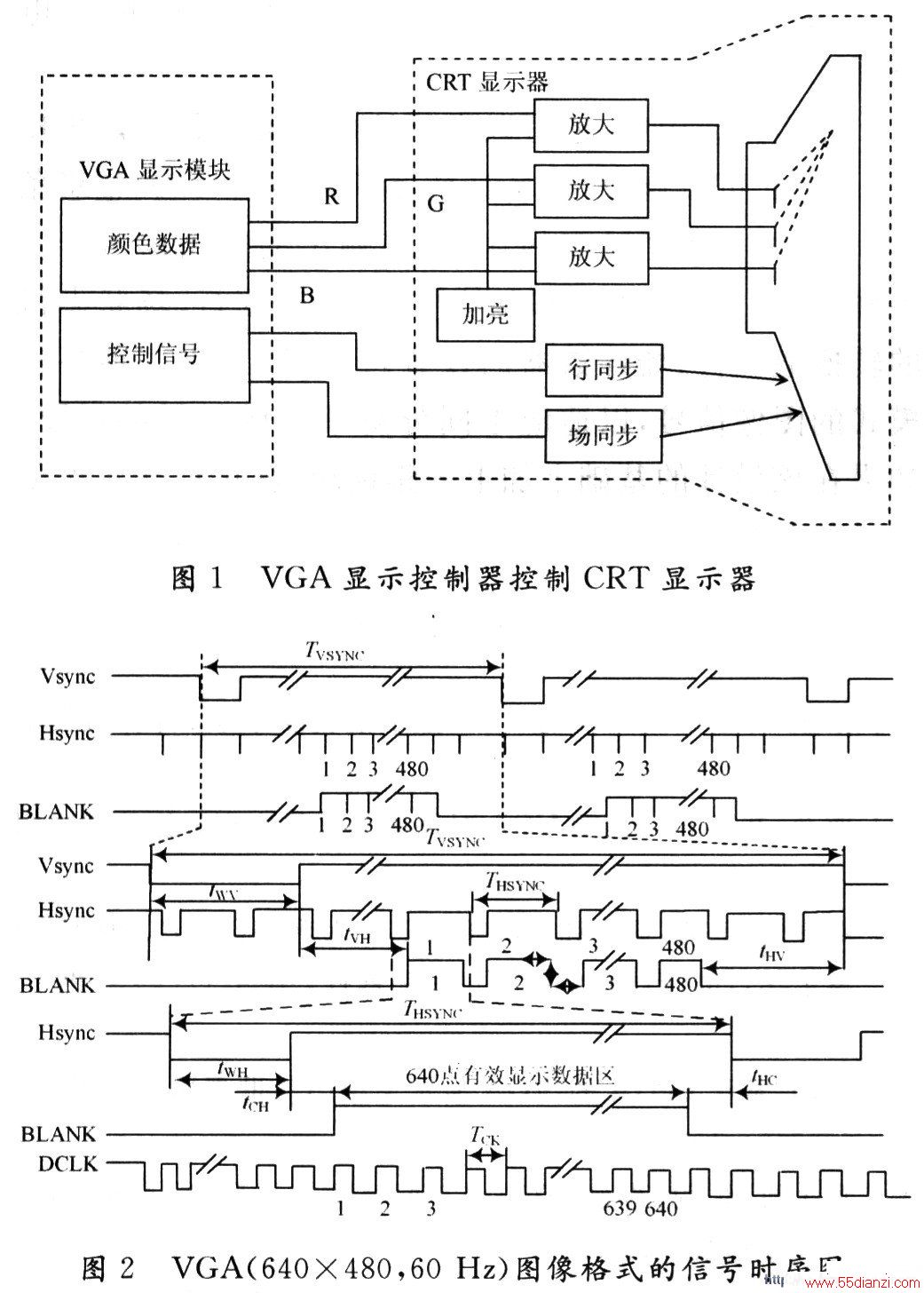

常见的彩色显示器一般由阴极射线管(CRT)构成,彩色由GRB(Green Red Blue)基色组成。显示采用逐行扫描的方式解决,阴极射线枪发出电子束打在涂有荧光粉的荧光屏上,产生GRB基色,合成一个彩色像素。扫描从屏幕的左上方开始,从左到右,从上到下,逐行扫描,每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT、对电子束进行消隐,每行结束时,用行同步信号进行行同步;扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,并预备进行下一次的扫描。VGA显示控制器控制 CRT显示图象的过程如图1所示。

2 VGA信号时序

图2所示是计算机VGA(640×480,60 Hz)图像格式的信号时序图。图2中,V_sync为场同步信号,场周期TVSYNC=16.683 ms,每场有525行,其中480行为有效显示行,45行为场消隐期。场同步信号Vs中每场有1个脉冲,该脉冲的低电平宽度tWV=63μs(2行)。场消隐期包括场同步时间tWH、场消隐前肩tHV(13行)、场消隐后肩tVH(30行),共45行。行周期THSYNC=31.78μs,每显示行包括 800点。其中,640点为有效显示区,160点为行消隐期(非显示区)。行同步信号Hs中每行有一个脉冲,该脉冲的低电平宽度tWV=3.81 μs(即96个DCK);行消隐期包括行同步时间tWH,行消隐前肩tHC(19个DCLK)和行消隐后肩tCH(45个DCLK),共160个点时钟。复合消隐信号是行消隐信号和场消隐信号的逻辑与,在有效显示期复合消隐信号为高电平,在非显示区域它是低电平。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术