摘要:基于FIR数字滤波器的原理和层次化、模块化设计思想,结合ALTEra公司的CycloneII系列FPGA芯片,提出了FIR数字滤波器的实现硬件方案,给出了采用Matlab、QUARTusⅡ设计及实现32阶低通FIR滤波器的方法步骤,仿真及实际测试结果验证了设计方案的正确性,与传统的数字滤波器相比,本文设计的FIR数字滤波器具有更好的实时性、灵活性和实用性。

关键词:FIR数字滤波器;FPGA;Verilog HDL;Matlab

1 引 言

FIR数字滤波器以其良好的线性特性被广泛应用于现代电子通信系统中,是数字信号处理的重要内容之一。在实际信号处理中,往往要求系统兼具实时性和灵活性,而已有的一些软件或硬件实现方案(如DSP)则难以同时达到这两方面的要求。使用具有并行处理特性的FPGA来实现FIR滤波器,既有很强的实时性,又兼顾了灵活性,为数字信号处理提供了一种很好的解决方案。FIR滤波器系数计算较为繁琐,在设计时借助Matlab工具箱,选择合适的窗函数,可以方便地计算滤波器系数,并分析其幅频、相频特性。

本文在用FPGA设计FIR滤波器时,采用了层次化、模块化的设计思想,将整个滤波器划分为若干功能模块,运用Verilog HDL语言和原理图两种设计输入方式,各个模块先独立设计,验证无误后再互联综合,完成了FIR数字滤波器的系统设计及仿真测试。

2 FIR滤波器基本原理及结构

FIR数字滤波器的冲击响应h(n)为实序列时,频率响应:

![]()

若要求线性相位,则需:

![]()

因而h(n)如果满足对称或反对称的条件,就具有线性相位特性,即:

![]()

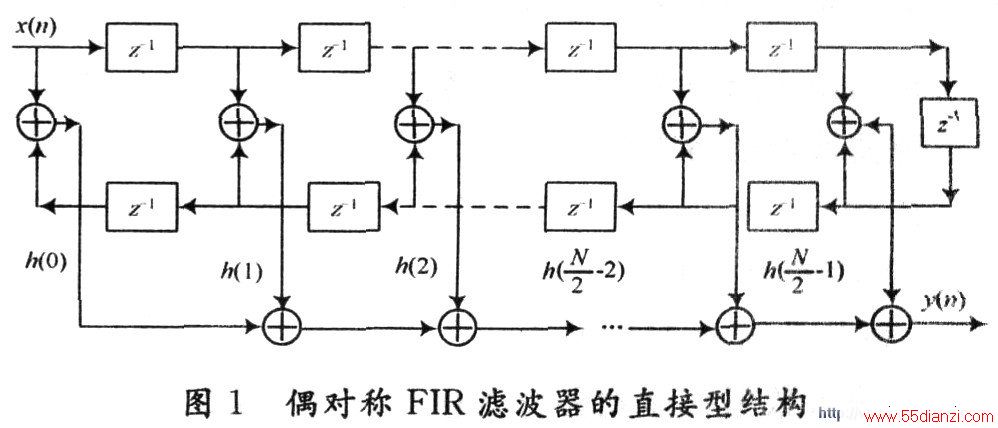

数字滤波器结构有很多种,偶对称FIR滤波器的直接型结构如图1所示。

其中x(n),y(n)分别为输入输出时间序列。容易得到32阶偶对称FIR滤波器的输入输出关系,如式(4)所示:

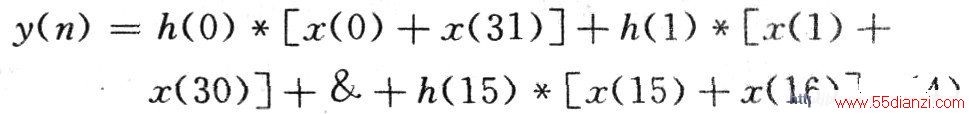

根据以上分析,可以把对称结构的FIR数字滤波器分成“移位相加单元、乘法器、输出相加及截位输出”四块,如图2所示。

对于长度为2M的滤波器,其运算次数只有M量级,减少了乘法次数,也提高了运算速度。在用FPGA实现时可以节约不少资源。

3 用Matlab设计FIR数宇滤波器

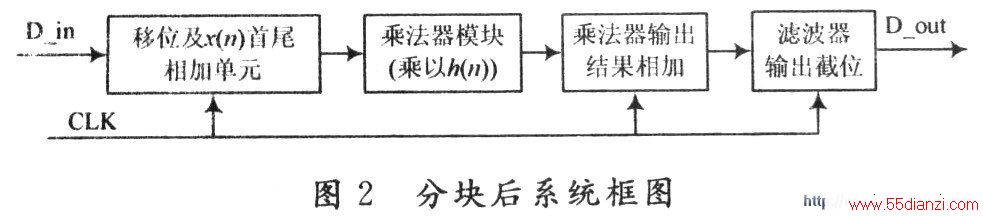

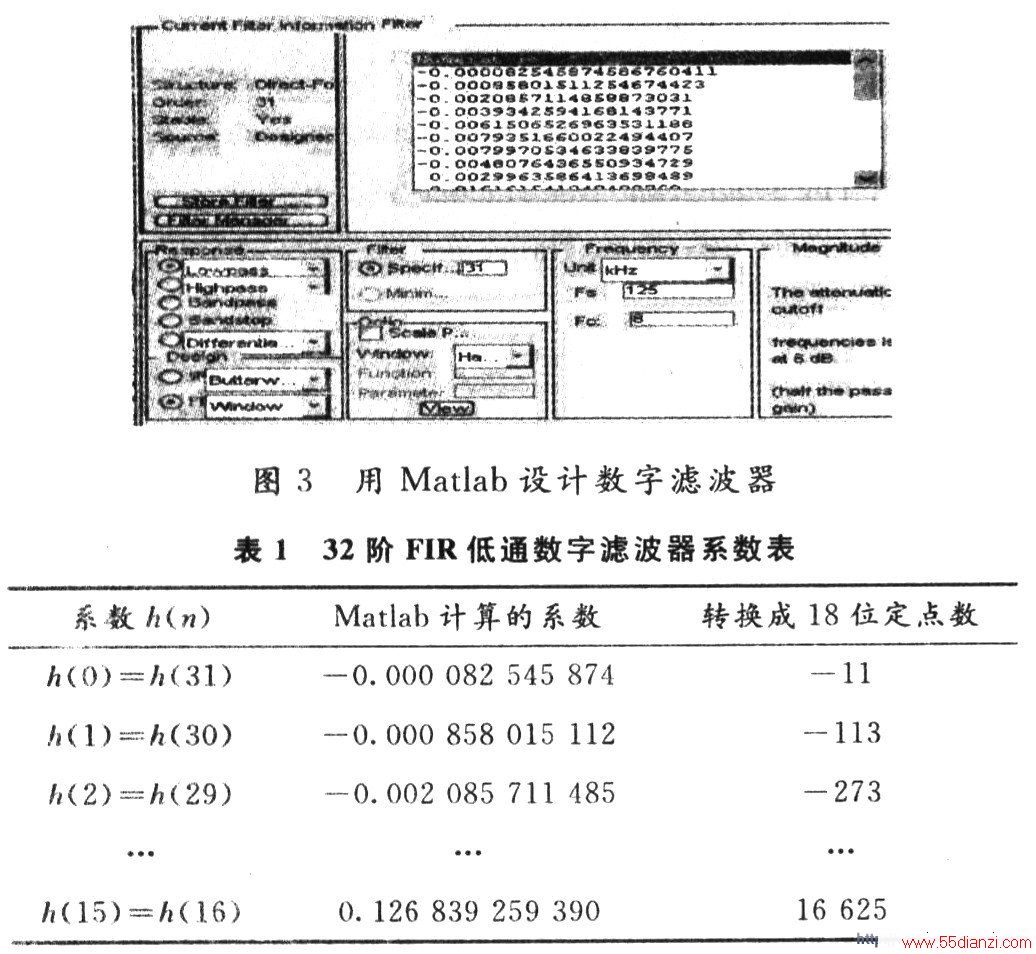

具有对称结构的直接型FIR滤波器结构如图1所示,用加窗的设计方法,经比较后窗函数选用海明窗。根据实际指标要求在Matlab的“Filter Design”工具里设置各参数,然后算得系数h(n),如图3所示,得到的系数是用十进制表示的,需要将其转换成系统要求精度(如18位)的定点二进制小数。把所有系数乘以218后再四舍五入即可,最终数据如表1所示。

4 滤波器的FPGA实现及仿真测试

按照图l、图2和滤波器系数表1,用Verilog HDL分别实现滤波器的各个模块,仿真无误后生成单元模块图,然后在QuartusⅡ里调用该模块,互联后综合得到系统电路图,各功能模块的设计方法如下。

4.1 移位及首尾相加单元

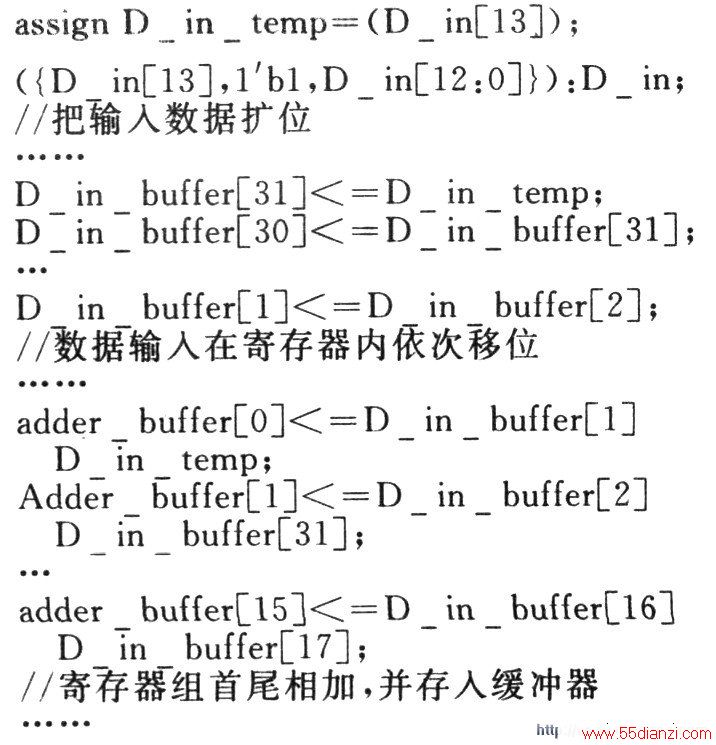

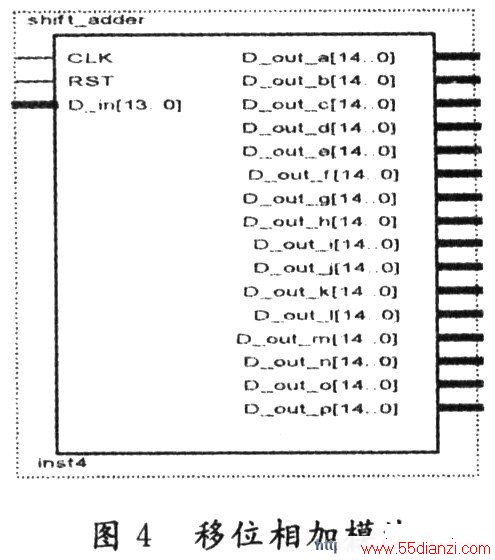

把输入数据存储到移位寄存器,利用FIR滤波器的对称性,把移位后的数据首尾相加即可。加法器输出端要加个寄存器模块,以去除毛刺。另外为防止相加后数据溢出,要把数据位数扩宽到14+1位。其中D_in[13..O]是二进制补码输入,D out XX[14..O]是移位相加后数据输出。Vexrilog HDL程序关键语句为:

移位相加单元模块图如图4所示。

本文关键字:滤波器 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术